Machine Translated by Google

# CX32L003

# ARM® Cortex® -M0+ 32-bit Microcontroller User

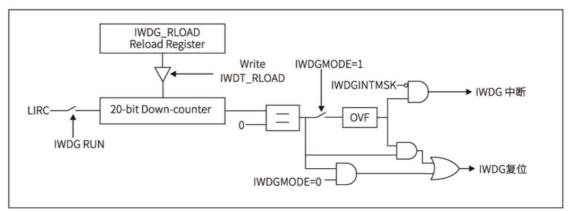

## **Reference Manual**

#### Table of contents

| Figure index                           | 27 |

|----------------------------------------|----|

| table index                            |    |

| 1 Introduction                         |    |

| 2Product features                      | 37 |

| 3 Overview of product functions        | 38 |

| 3.1 32- bit Cortex® -M0+ core          |    |

| 3.2Memory                              | 38 |

| 3.2.1 Embedded flash memory (Flash)    |    |

| 3.2.2 Built-in SRAM                    |    |

| 3.3 Clock system                       |    |

| 3.4 Working mode                       |    |

| 3.5 Interrupt Controller (NVIC)        | 40 |

| 3.6 Resetting the controller           | 41 |

| 3.7 General-purpose I/O port (GPIO)    | 41 |

| 3.8 Timers and Watchdog                | 41 |

| 3.8.1 Advanced Control Timer (TIM1)    | 42 |

| 3.8.2 General purpose timer (TIM2)     | 42 |

| 3.8.3 Programmable Counter Array (PCA) | 42 |

| 3.8.4 Low Power Timer (LPTIM)          | 42 |

| 3.8.5 Basic timer (TIM10/TIM11)42      |    |

| 3.8.6 Independent Watchdog (IWDG)      | 43 |

| 3.8.7 System Window Watchdog (WWDG)    | 43 |

| 3.8.8 SysTick timer (SYST)             | 43 |

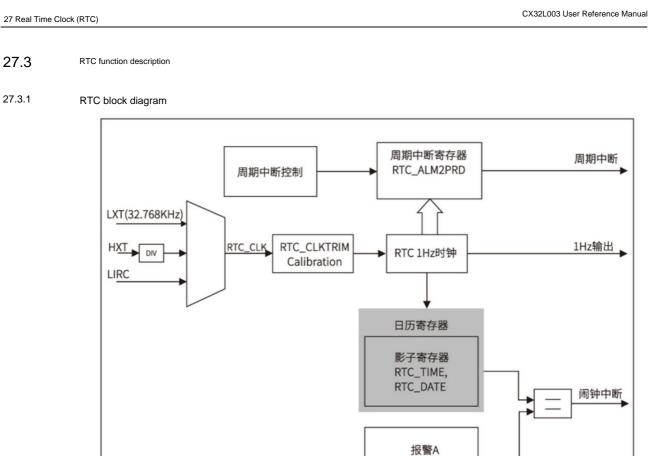

| 3.9 Real Time Clock (RTC)                                  | 43 |

|------------------------------------------------------------|----|

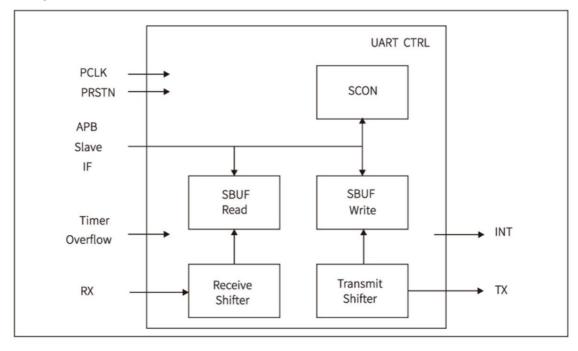

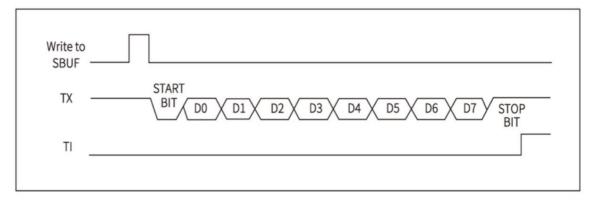

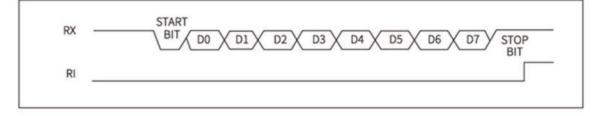

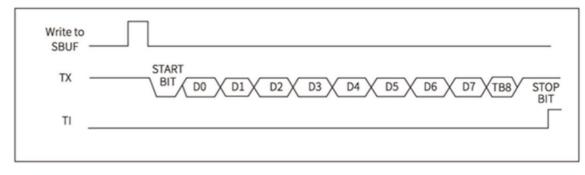

| 3.10 Universal Asynchronous Transceiver (UART0/UART1)      |    |

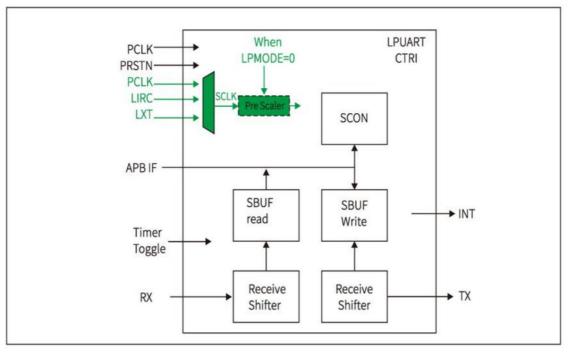

| 3.11 Low Power Universal Asynchronous Transceiver (LPUART) | 43 |

| 3.12 Serial Peripheral Interface (SPI)                     | 43 |

| 3.13 I2C interface (I2C)                                   |    |

| 3.14 One-Wire Interface (OWIRE)ÿ                           | 44 |

| 3.15 Buzzer (BEEP)                                         | 44 |

| 3.16 Self-wake-up timer (AWK)                              | 4  |

| 3.17 Clock Calibration/Monitoring Module (CLKTRIM)         | 44 |

| 3.18 Unique ID number (UID)                                | 44 |

| 3.19 Cyclic Redundancy Check Calculation Unit (CRC)        |    |

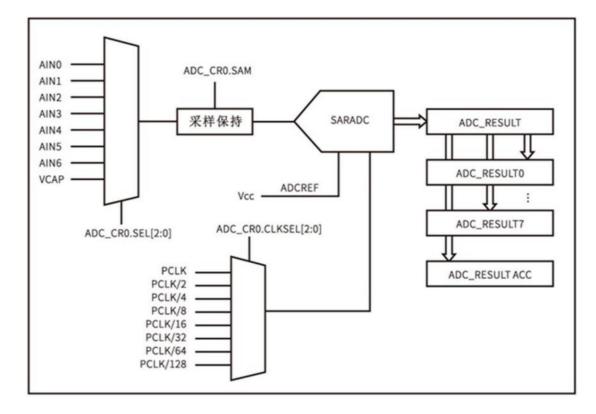

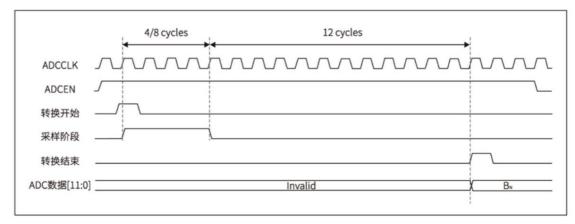

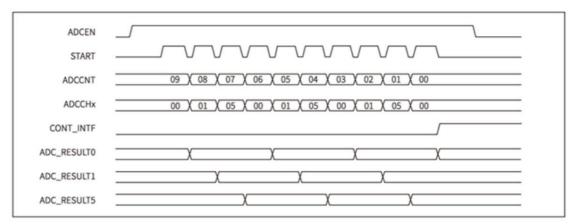

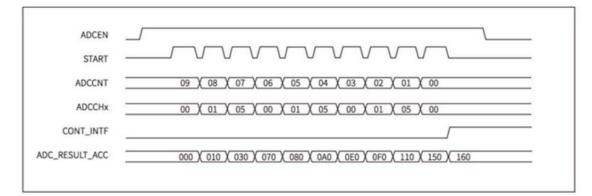

| 3.20 Analog/Digital Converter (ADC)                        | 45 |

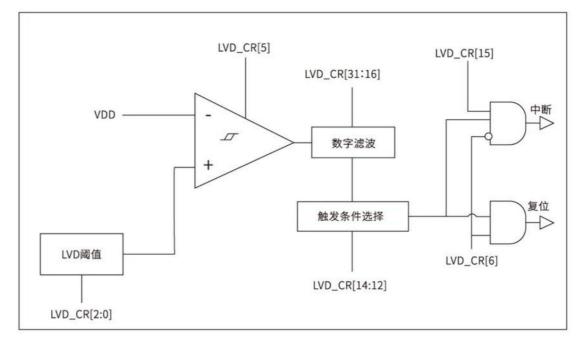

| 3.21 Low Voltage Detector (LVD)                            | 45 |

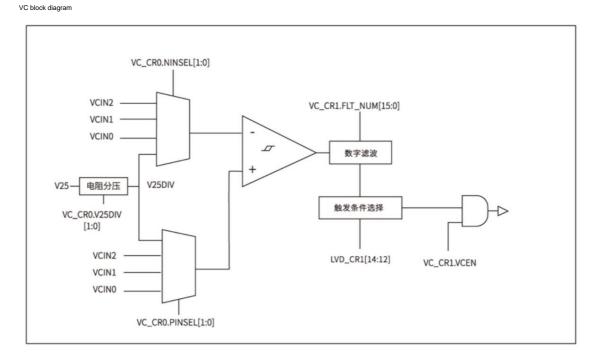

| 3.22 Voltage Comparator (VC)                               | 45 |

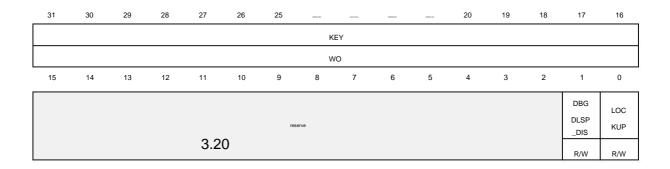

| 3.23 Embedded debugging system 45                          |    |

| 3.24 Encrypted Embedded Debug Support (DBG)                | 45 |

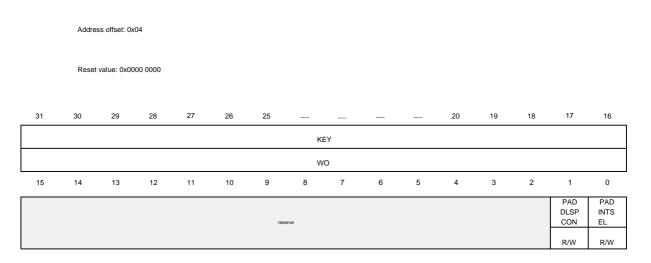

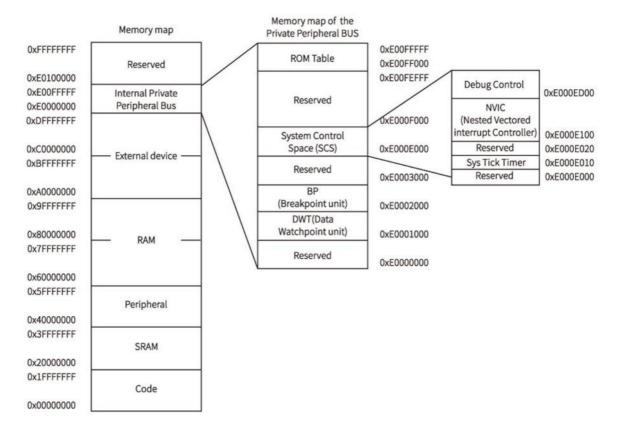

| 4 System and Memory Overview                               | 46 |

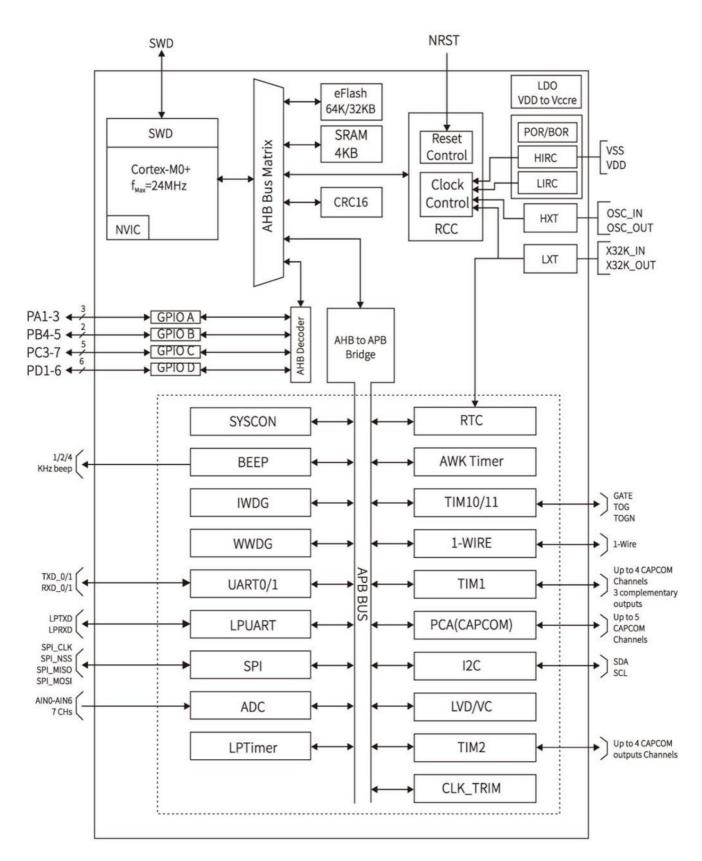

| 4.1 System architecture diagram                            | 46 |

| 4.2 Memory Mapping                                         | 48 |

| 4.3 Memory space and module address                        | 49 |

| 4.4 Embedded SRAM                                          | 50 |

| <sup>4.5</sup> Flash memory                                | 50 |

| 4.5.1 Embedded bootloader (Bootloader)                     | 50 |

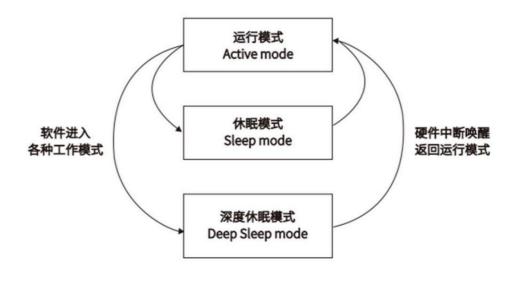

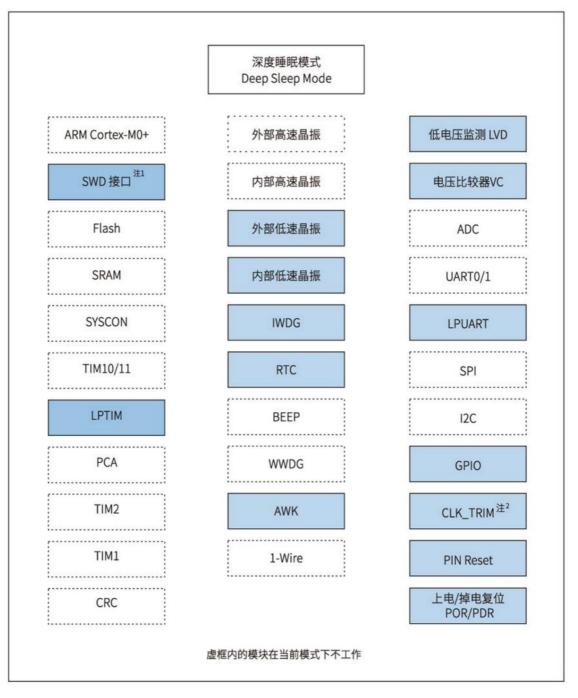

| 5 Working modes and power management                       | 51 |

| 5.1 Operation mode (Active Mode)                           | 51 |

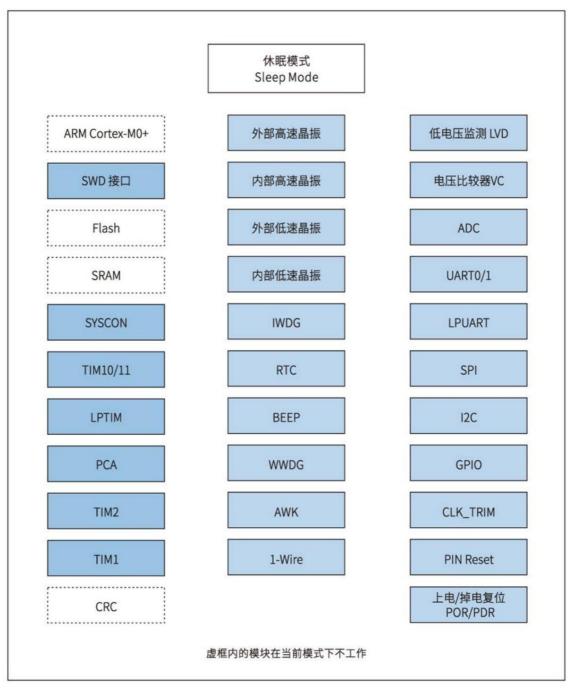

| 5.2 Sle  | ep Mode (Sleep Mode)                                     |    |

|----------|----------------------------------------------------------|----|

| 5.3 De   | ep Sleep Mode (Deep Sleep Mode)                          |    |

| 5.4      | Cortex® -M0+ Core System Control Register (SCR)          |    |

| 6 Syster | m reset and clock (RCC)                                  |    |

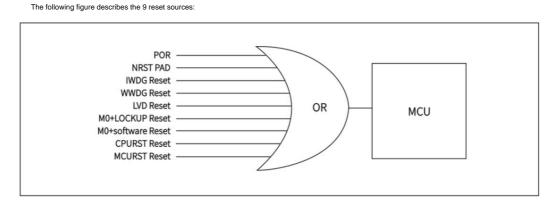

| 6.1 Re:  | set                                                      |    |

| 6.1.1    | Introduction to Reset Controller                         |    |

| 6.1.2    | Reset source                                             |    |

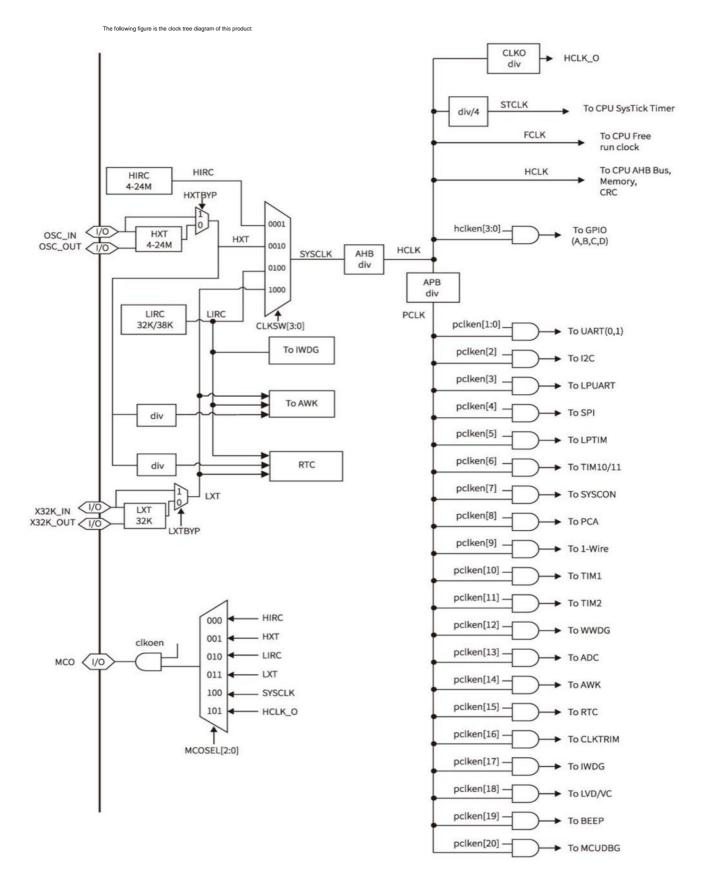

| 6.2 Sys  | stem Clock                                               | 60 |

| 6.2.1    | System Clock Tree                                        | 61 |

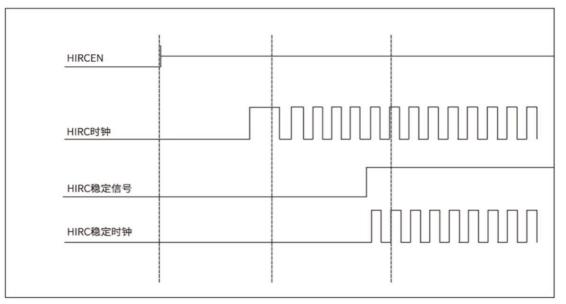

| 6.2.2    | Internal high speed RC clock HIRC                        | 62 |

| 6.2.3    | Internal low-speed RC clock LIRC                         | 62 |

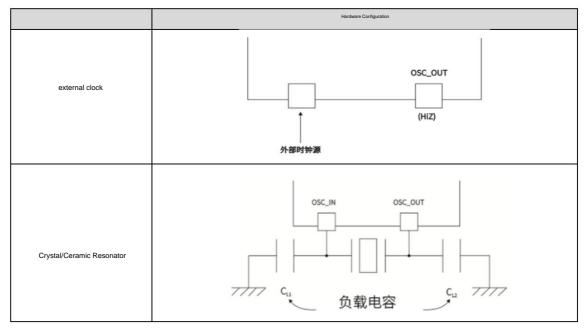

| 6.2.4    | External high-speed crystal oscillator clock HXT         |    |

| 6.2.5    | External low-speed crystal oscillator clock LXT          | 63 |

| 6.2.6    | System clock start-up process                            |    |

| 6.2.7    | System Clock Switching                                   | 63 |

| 6.2.8    | System Clock Output                                      |    |

| 6.2.9    | System Clock Security Control                            | 65 |

| 6.2.10   | ) IWDG clock                                             | 65 |

| 6.2.11   | 1 RTC clock                                              | 65 |

| 6.2.12   | 2 AWK clock                                              |    |

| 6.2.13   | 3 Low power consumption mode                             |    |

| 6.3 Re   | gister list                                              | 66 |

| 6.4 Re   | gister Description                                       | 67 |

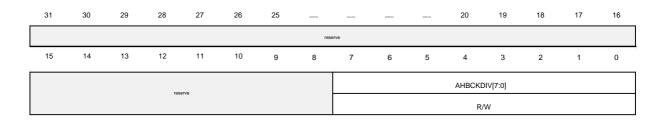

| 6.4.1    | AHB Clock Divider Register (RCC_HCLKDIV)                 | 67 |

| 6.4.2    | APB Clock Frequency Divider Register (RCC_PCLKDIV)       | 67 |

| 6.4.3    | AHB Peripheral Module Clock Enable Register (RCC_HCLKEN) |    |

| Talà d'orana                                                                 | CX32L003 User Reference Manual |

|------------------------------------------------------------------------------|--------------------------------|

| 6.4.4 APB Peripheral Module Clock Enable Register (RCC_PCLKEN)               | 69                             |

| 6.4.5 Clock Output Control Register (RCC_MCOCR)                              | 71                             |

| 6.4.6 System reset control register (RCC_RSTCR)                              |                                |

| 6.4.7 System reset status register (RCC_RSTSR)                               |                                |

| 6.4.8 System clock source configuration register (RCC_SYSCLKCR)              | 74                             |

| 6.4.9 System clock source selection register (RCC_SYSCLKSEL)                 |                                |

| 6.4.10 Internal High Speed RC Oscillator Control Register (RCC_HIRCCR)       |                                |

| 6.4.11 External High Speed Crystal Oscillator Control Register (RCC_HXTCR)   |                                |

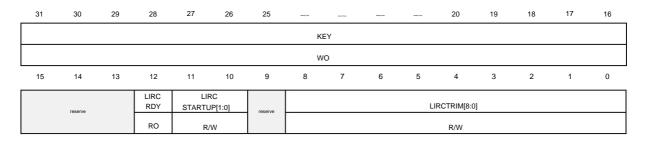

| 6.4.12 Internal Low-Speed RC Oscillator Control Register (RCC_LIRCCR)        | 78                             |

| 6.4.13 External low-speed crystal oscillator control register (RCC_LXTCR)    | 79                             |

| 6.4.14 Cortex M0+ IRQ Latency Control Register (RCC_IRQLATENCY)              | 80                             |

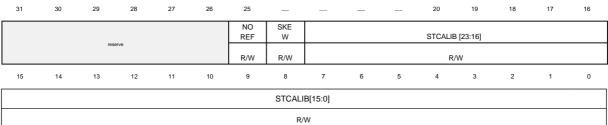

| 6.4.15 SysTick Timer Control Register (RCC_STICKCR)                          |                                |

| 6.4.16 SWDIO Port Control Register (RCC_SWDIOCR)                             | 81                             |

| 6.4.17 Peripheral module reset control register (RCC_PERIRST)                | 82                             |

| 6.4.18 RTC Reset Control Register (RCC_RTCRST)                               |                                |

| 6.4.19 Register write protection control register (RCC_UNLOCK)               | 84                             |

| 7 System Control (SYSCON)                                                    | 85                             |

| 7.1 Register list                                                            |                                |

| 7.2 Register description                                                     |                                |

| 7.2.1 System Configuration Register 0 (SYSCON_CFGR0)                         |                                |

| 7.2.2 Terminal Deep Sleep Interrupt Mode Control Register (SYSCON_PORTINTCR) | 87                             |

| 7.2.3 Terminal Control Register (SYSCON_PORTCR)                              |                                |

| 7.2.4 PCA Capture Channel Control Register (SYSCON_PCACR)                    |                                |

| 7.2.5 TIM1 channel input source selection (SYSCON_TIM1CR)                    | 90                             |

| 7.2.6 TIM2 channel input source selection (SYSCON_TIM2CR)                    | 92                             |

| 7.2.7 Syscon register write protection (SYSCON_UNLOCK)                       | 93                             |

Table of contents

| 8 Interrupt  | Controller (NVIC)                                                             |                 | 94   |

|--------------|-------------------------------------------------------------------------------|-----------------|------|

| 8.1 Overvie  | ЭW                                                                            | 94              |      |

| 8.2 Feature  | əs                                                                            | 94              |      |

| 8.3 Interrup | ot Priority                                                                   |                 | . 94 |

| 8.4 Interrup | ot vector table                                                               |                 | 95   |

| 8.5 Interrup | ot Wakeup Control WIC                                                         |                 | 96   |

| 8.5.1 NVI    | C wakes up from deep sleep mode and enters interrupt ISR setting              | 96              |      |

| 8.5.2 NVI    | C wake-up from deep sleep mode setting does not execute interrupt ISR setting |                 | 96   |

| 8.5.3        | Using the Exit Hibernate Feature                                              |                 | 97   |

| 8.6 Basic c  | operation of the software                                                     |                 |      |

| 8.6.1        | External Interrupt Enable                                                     | 98              | ;    |

| 8.6.2 NVI    | C interrupt enable and clear enable                                           | 98              |      |

| 8.6.3 NVI    | C interrupt pending and clear pending                                         | 98              |      |

| 8.6.4 NVI    | C Interrupt Priority                                                          | 98              |      |

| 8.6.5 NVI    | C Interrupt Masking                                                           | 99              |      |

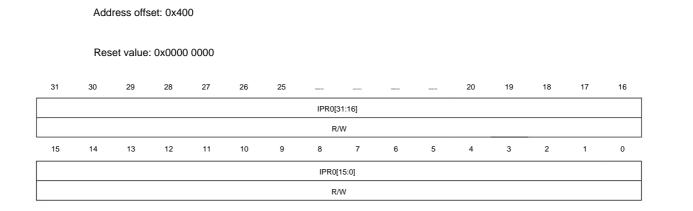

| 8.7 Registe  | er list                                                                       | . 100           |      |

| 8.8 Registe  | er description                                                                | 10 <sup>.</sup> | 1    |

| 8.8.1        | Interrupt Enable Setting Register (NVIC_ISER)                                 | 101             |      |

| 8.8.2        | Interrupt Enable Clear Register (NVIC_ICER)                                   | 101             |      |

| 8.8.3        | Interrupt Pending Setup Register (NVIC_ISPR)                                  |                 | 02   |

| 8.8.4        | Interrupt Pending Clear Register (NVIC_ICPR)                                  | 102             |      |

| 8.8.5        | Interrupt Priority Control Register 0 (NVIC_IPR0)                             | 103             |      |

| 8.8.6        | Interrupt Priority Control Register 1 (NVIC_IPR1)                             | 103             |      |

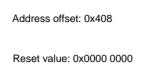

| 8.8.7        | Interrupt Priority Control Register 2 (NVIC_IPR2)                             | 104             |      |

| 8.8.8        | Interrupt Priority Control Register 3 (NVIC_IPR3)                             | 104             |      |

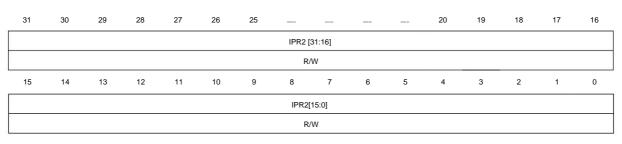

| 8.8.9        | Interrupt Priority Control Register 4 (NVIC_IPR4)                             | 105             |      |

| 8.8.10    | Interrupt Priority Control Register 5 (NVIC_IPR5)105              |     |       |

|-----------|-------------------------------------------------------------------|-----|-------|

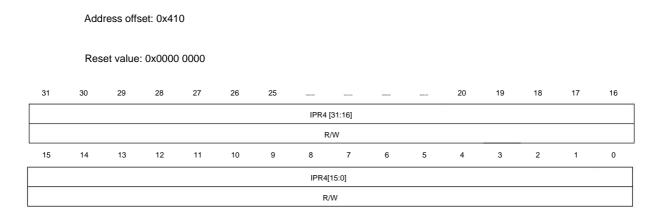

| 8.8.11    | Interrupt Priority Control Register 6 (NVIC_IPR6)106              |     |       |

| 8.8.12    | Interrupt Priority Control Register 7 (NVIC_IPR7)106              |     |       |

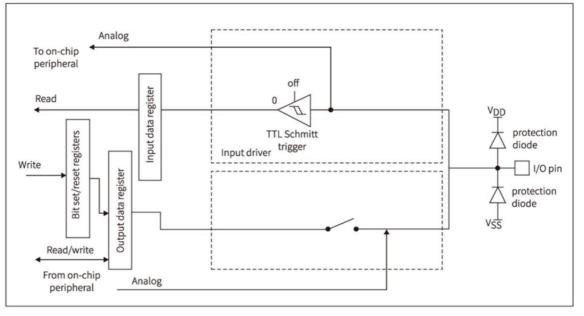

| 9 general | -purpose input and output (GPIO)                                  |     | 107   |

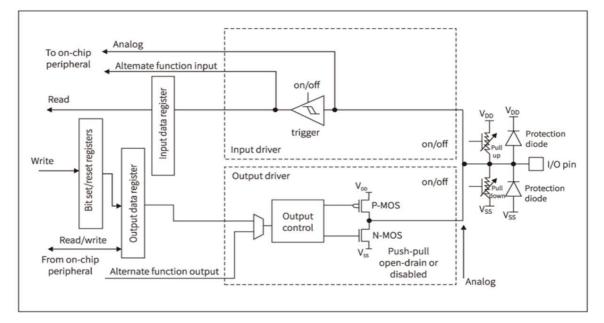

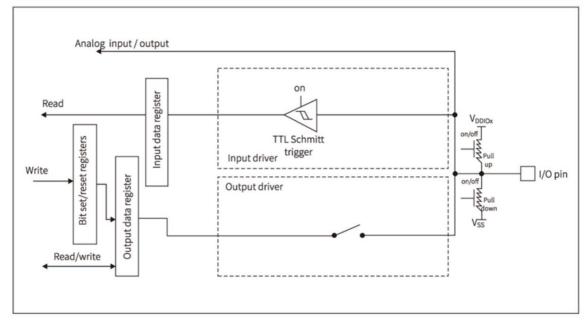

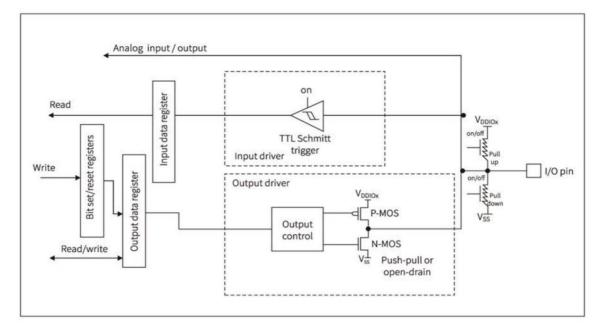

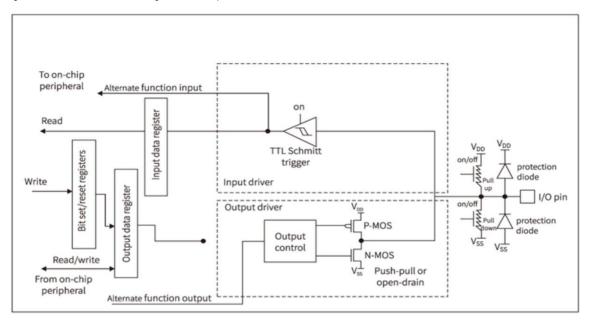

| 9.1       | Introduction to GPIOs                                             | 107 |       |

| 9.2       | GPIO main features                                                | 107 |       |

| 9.3       | GPIO Functional Description                                       |     | . 108 |

| 9.3.1 (   | General-purpose I/O (GPIO)                                        | 110 |       |

| 9.3.2     | I/O PORT CONTROL REGISTER                                         |     | 110   |

| 9.3.3     | I/O Port Data Registers                                           | 110 |       |

| 9.3.4     | I/O Data Bit Handling                                             | 111 |       |

| 9.3.5     | Input Configuration                                               | 111 |       |

| 9.3.6     | Output Configuration                                              | 112 |       |

| 9.3.7 E   | xternal interrupt/wake-up line                                    | 112 |       |

| 9.3.8     | Alternate functions and remapping of I/O pins                     |     |       |

| 9.3.9     | Simulation Configuration                                          | 116 |       |

| 9.3.10    | HXT or LXT pin used as GPIO116                                    |     |       |

| 9.4       | GPIO Register List                                                | 117 |       |

| 9.5       | GPIO register description                                         | 118 |       |

| 9.5.1 (   | GPIO Port Direction Register (GPIOx_DIRCR)(x = AD)                | 118 |       |

| 9.5.2 0   | GPIO port output type register (GPIOx_OTYPER) (x = AD)119         |     |       |

| 9.5.3 (   | SPIO Port Output Data Register (GPIOx_ODR)(x = AD)120             |     |       |

| 9.5.4 0   | SPIO Port Input Data Register (GPIOx_IDR)(x = AD)121              |     |       |

| 9.5.5 0   | GPIO Port Interrupt Enable Register (GPIOx_INTEN)(x = AD)1        | 22  |       |

| 9.5.6 0   | GPIO Port Interrupt Raw Status Register (GPIOx_RAWINTSR) (x = AD) |     |       |

| 9.5.7 (   | GPIO Port Interrupt Status Register (GPIOx_MSKINTSR) (x = AD)     | 124 |       |

| 9.5.8 GPIO Port Interrupt Clear Register (GPIOx_INTCLR)(x = AD)                                                                                                                                                                                                                                                                                                    | 125            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 9.5.9 GPIO Port Interrupt Type Register (GPIOx_INTTYPCR) (x = AD)                                                                                                                                                                                                                                                                                                  | 126            |

| 9.5.10 GPIO Port Interrupt Type Register (GPIOx_INTPOLCR) (x = AD)                                                                                                                                                                                                                                                                                                 | 127            |

| 9.5.11 GPIO port any edge trigger interrupt register (GPIOx_INTANY)(x = AD)                                                                                                                                                                                                                                                                                        | 128            |

| 9.5.12 GPIO port output set register (GPIOx_ODSET) (x = AD)1                                                                                                                                                                                                                                                                                                       | 29             |

| 9.5.13 GPIO Port Output Clear Register (GPIOx_ODCLR)(x = AD)                                                                                                                                                                                                                                                                                                       | 130            |

| 9.5.14 GPIO Port Input Debounce Register (GPIOx_INDBEN)(x = AD)                                                                                                                                                                                                                                                                                                    | 131            |

| 9.5.15 GPIO Port Input Debounce Clock Configuration Register (GPIOx_DBCLKCR)(x = AD)                                                                                                                                                                                                                                                                               | 132            |

| 9.5.16 GPIO Port Pull-Up/Pull-Down Register (GPIOx_PUPDR)(x = AD)                                                                                                                                                                                                                                                                                                  | 133            |

| 9.5.17 GPIO port voltage slew rate configuration (GPIOx_SLEWCR)(x = AD)                                                                                                                                                                                                                                                                                            | 134            |

| 9.5.18 GPIO port drive strength configuration register (GPIOx_DRVCR) (x = AD)                                                                                                                                                                                                                                                                                      | 135            |

| 9.5.19 GPIO Port Alternate Function Register (GPIOx_AFR)(x = AD)                                                                                                                                                                                                                                                                                                   | 136            |

| 10 Flash controller (Flash)                                                                                                                                                                                                                                                                                                                                        |                |

|                                                                                                                                                                                                                                                                                                                                                                    |                |

| 10.1 Flash Controller Overview                                                                                                                                                                                                                                                                                                                                     | 142            |

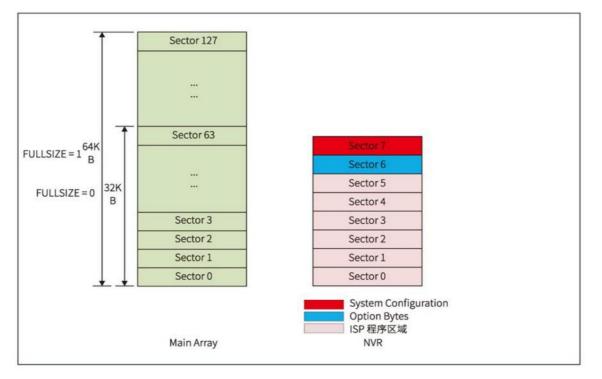

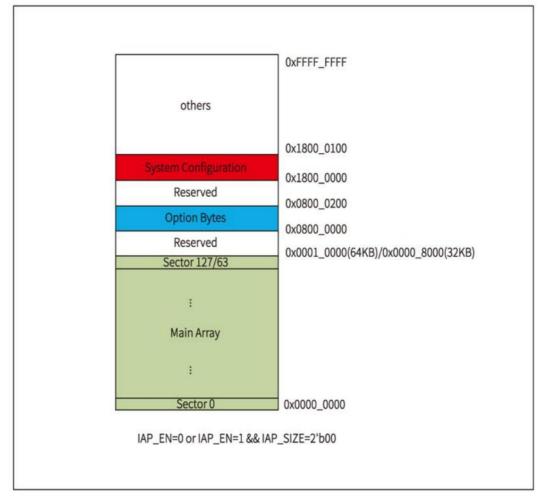

| 10.1    Flash Controller Overview      10.2 Flash Structure Diagram.                                                                                                                                                                                                                                                                                               |                |

|                                                                                                                                                                                                                                                                                                                                                                    | 142            |

| 10.2 Flash Structure Diagram                                                                                                                                                                                                                                                                                                                                       | 142            |

| 10.2 Flash Structure Diagram                                                                                                                                                                                                                                                                                                                                       | 142<br>143<br> |

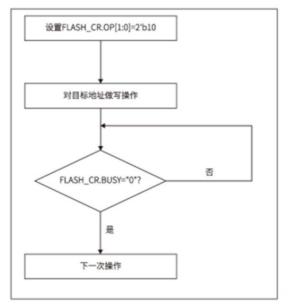

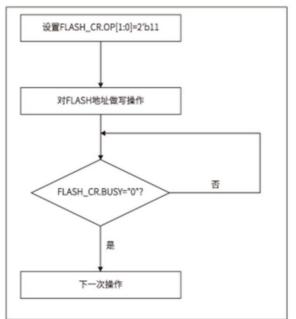

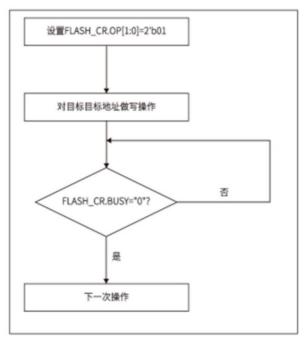

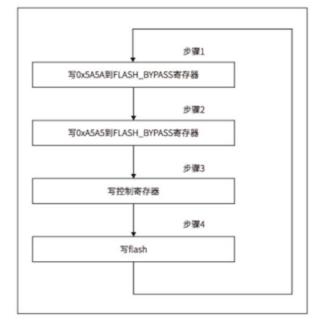

| 10.2 Flash Structure Diagram.         10.3 Function description         10.3.1 Erase Operation.                                                                                                                                                                                                                                                                    | 142<br>143<br> |

| 10.2 Flash Structure Diagram.         10.3 Function description         10.3.1 Erase Operation.         10.3.2 Write operation.                                                                                                                                                                                                                                    | 142<br>143<br> |

| 10.2 Flash Structure Diagram.         10.3 Function description         10.3.1 Erase Operation.         10.3.2 Write operation.         10.3.3 Read operation.                                                                                                                                                                                                     |                |

| 10.2 Flash Structure Diagram.         10.3 Function description         10.3.1 Erase Operation.         10.3.2 Write operation.         10.3.3 Read operation.         10.3.4 Erase and write time.                                                                                                                                                                |                |

| 10.2 Flash Structure Diagram.         10.3 Function description         10.3.1 Erase Operation.         10.3.2 Write operation.         10.3.3 Read operation.         10.3.4 Erase and write time.         10.3.5 Erase and write protection.                                                                                                                     |                |

| 10.2 Flash Structure Diagram.         10.3 Function description         10.3.1 Erase Operation.         10.3.2 Write operation.         10.3.3 Read operation.         10.3.4 Erase and write time.         10.3.5 Erase and write protection.         10.3.6 System BOOT address mapping.                                                                         |                |

| 10.2 Flash Structure Diagram.         10.3 Function description         10.3.1 Erase Operation.         10.3.2 Write operation.         10.3.3 Read operation.         10.3.4 Erase and write time.         10.3.5 Erase and write protection.         10.3.6 System BOOT address mapping.         10.3.7 Option Bytes                                             |                |

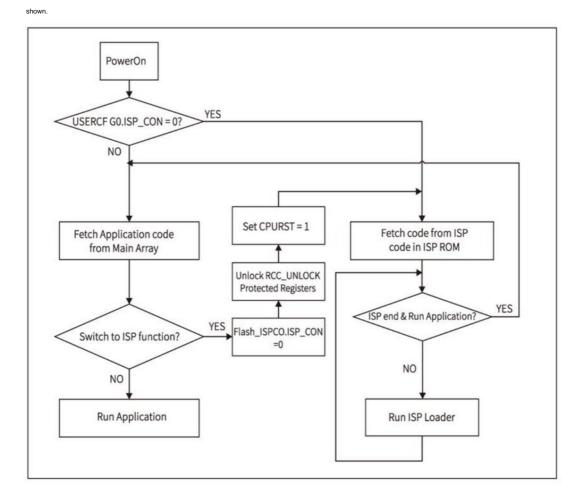

| 10.2 Flash Structure Diagram.         10.3 Function description         10.3.1 Erase Operation.         10.3.2 Write operation.         10.3.3 Read operation.         10.3.4 Erase and write time.         10.3.5 Erase and write protection.         10.3.6 System BOOT address mapping.         10.3.7 Option Bytes         10.3.8 In-System Programming (ISP). |                |

| 10.5.1 Flash_CR (Flash Control Register)                                                                                                        | 150                                        |

|-------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|

| 10.5.2 Flash_IFR (Flash Interrupt Flag Register)                                                                                                | 150                                        |

| 10.5.3 Flash_ICLR (Flash Interrupt Flag Clear Register)                                                                                         | 151                                        |

| 10.5.4 Flash_BYPASS (BYPASS sequence register)                                                                                                  | 151                                        |

| 10.5.5 Flash_SLOCK0 (sector erasing and writing protection register 0)                                                                          | 152                                        |

| 10.5.6 Flash_SLOCK1 (sector erasing and writing protection register 1)                                                                          | 154                                        |

| 10.5.7 Flash_ISPCON (Flash ISPCON configuration register)                                                                                       | 156                                        |

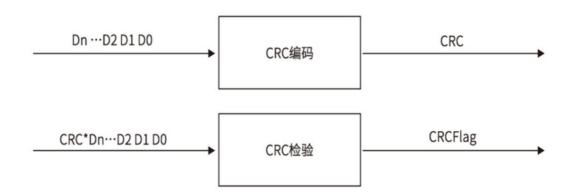

| 11 Cyclic Redundancy Check Calculation Unit (CRC)                                                                                               | 157                                        |

| 11.1 Overview                                                                                                                                   | 157                                        |

| 11.2 Function description                                                                                                                       | 157                                        |

| 11.2.1 CRC encoding mode                                                                                                                        | 157                                        |

| 11.2.2 CRC check mode                                                                                                                           | 158                                        |

| 11.3 Register list                                                                                                                              | 158                                        |

|                                                                                                                                                 |                                            |

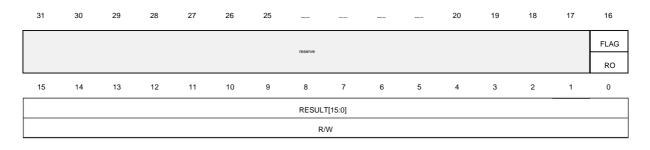

| 11.4 Register Description                                                                                                                       | 159                                        |

| 11.4 Register Description                                                                                                                       |                                            |

|                                                                                                                                                 | 159                                        |

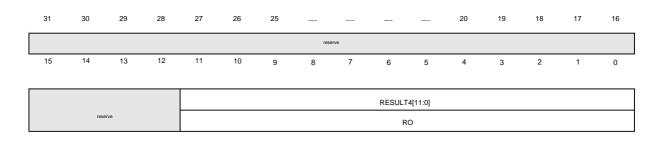

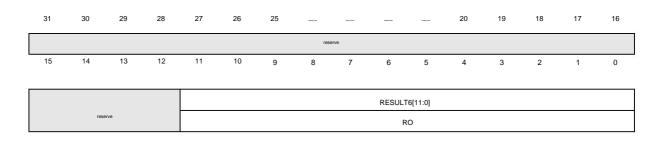

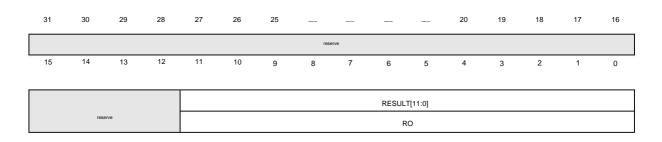

| 11.4.1 CRC result register (CRC_RESULT)                                                                                                         | 159<br>160                                 |

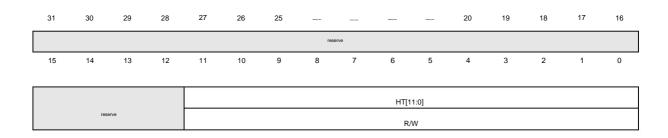

| 11.4.1 CRC result register (CRC_RESULT)                                                                                                         | 159<br>160<br>161                          |

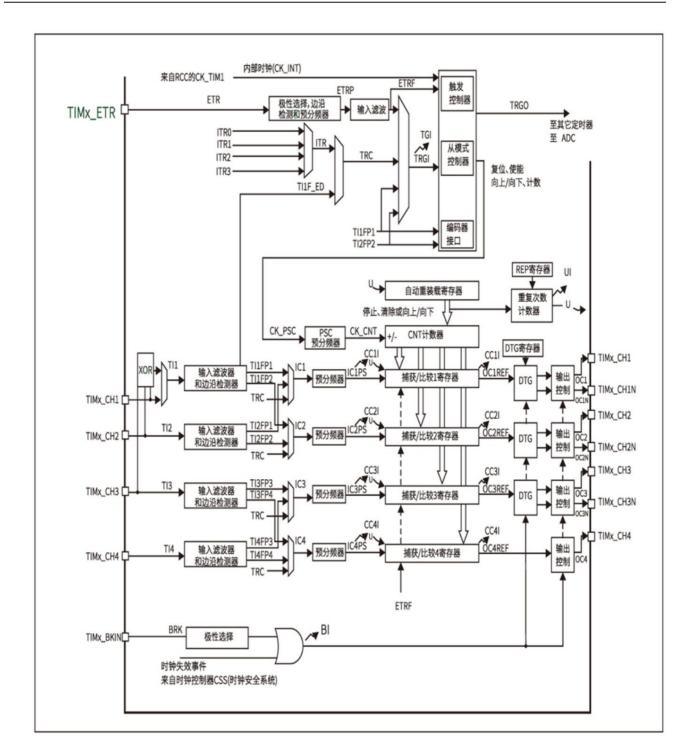

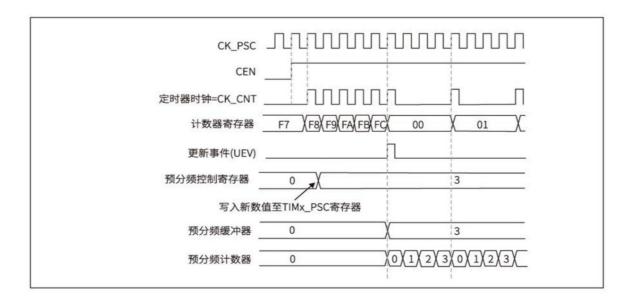

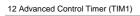

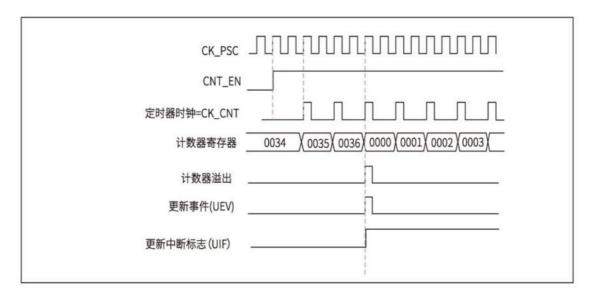

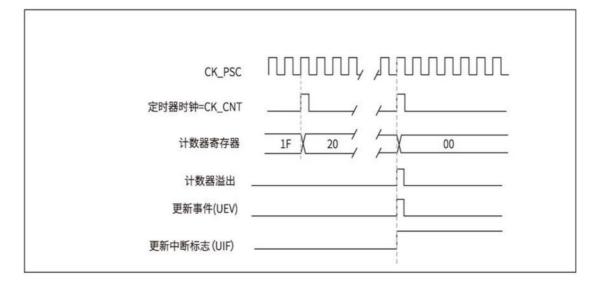

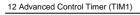

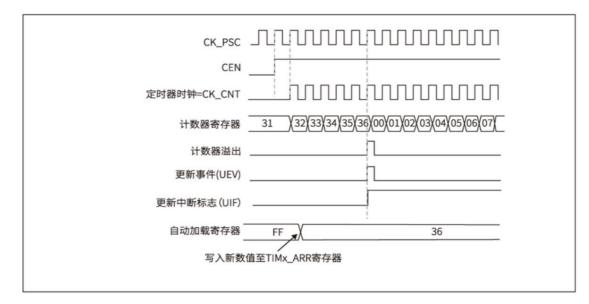

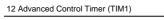

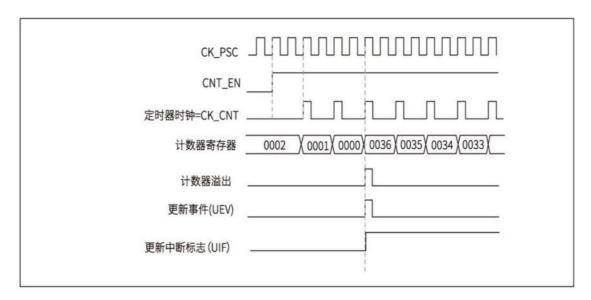

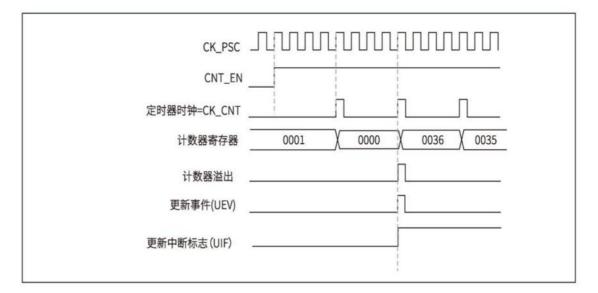

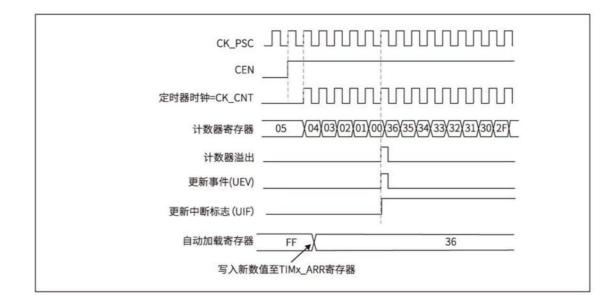

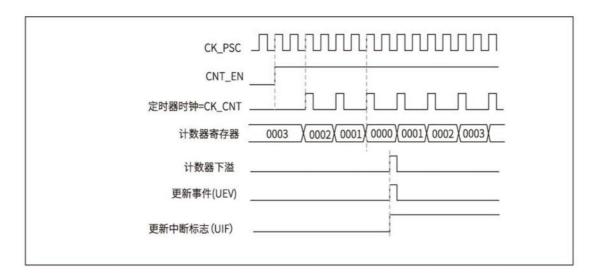

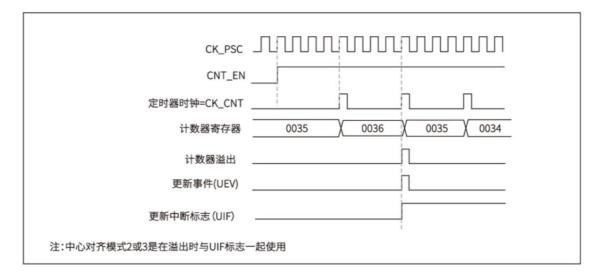

| 11.4.1 CRC result register (CRC_RESULT)<br>11.4.2 CRC data register (CRC_DATA)<br>12 Advanced Control Timer (TIM1)                              | 159<br>160<br>161<br>161                   |

| 11.4.1 CRC result register (CRC_RESULT)<br>11.4.2 CRC data register (CRC_DATA)<br>12 Advanced Control Timer (TIM1)<br>12.1 Introduction to TIM1 | 159<br>160<br>161<br>161<br>161            |

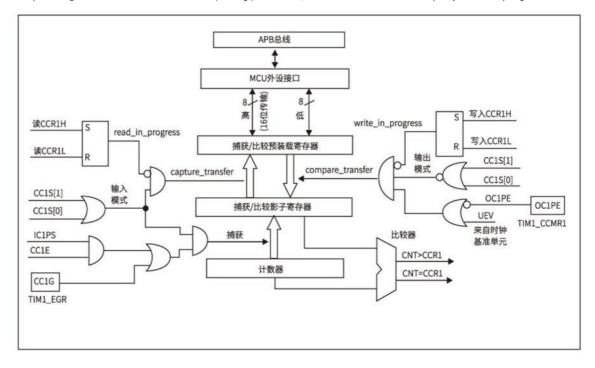

| <ul> <li>11.4.1 CRC result register (CRC_RESULT)</li></ul>                                                                                      | 159<br>160<br>161<br>161<br>161<br>163     |

| <ul> <li>11.4.1 CRC result register (CRC_RESULT)</li></ul>                                                                                      | 159<br>160<br>161<br>161<br>161<br>163<br> |

| 11.4.1 CRC result register (CRC_RESULT)                                                                                                         | 159<br>160<br>161<br>161<br>161<br>163<br> |

| 11.4.1 CRC result register (CRC_RESULT)                                                                                                         | 159<br>160<br>161<br>161<br>161<br>163<br> |

| 11.4.1 CRC result register (CRC_RESULT)                                                                                                         | 159<br>160<br>161<br>161<br>161<br>163<br> |

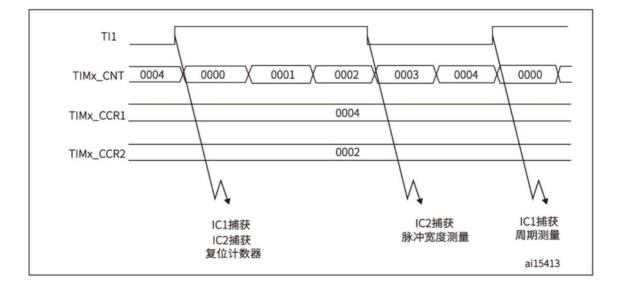

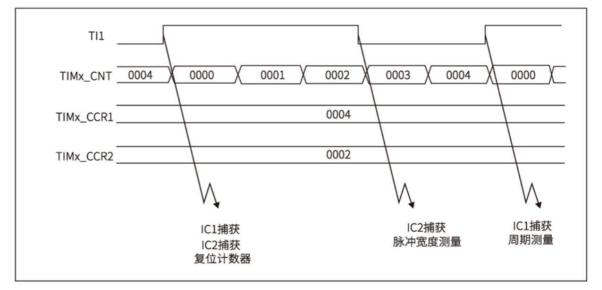

| 12.3.7 PWM input mode                                      |     |

|------------------------------------------------------------|-----|

| 12.3.8 Forced output mode                                  | 181 |

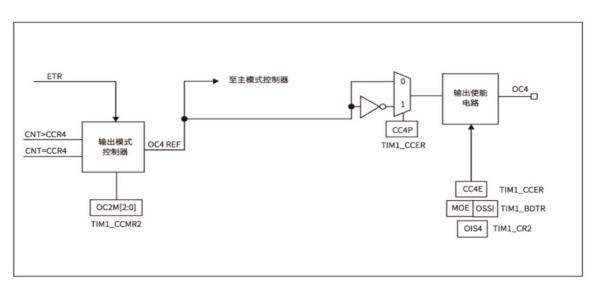

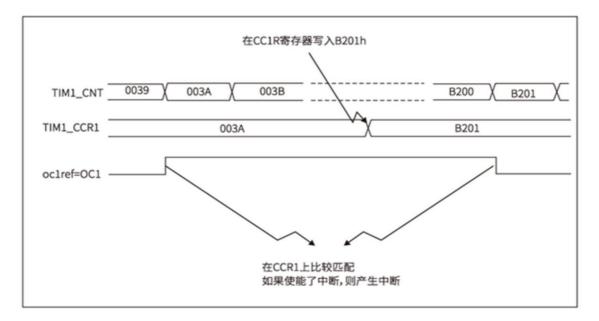

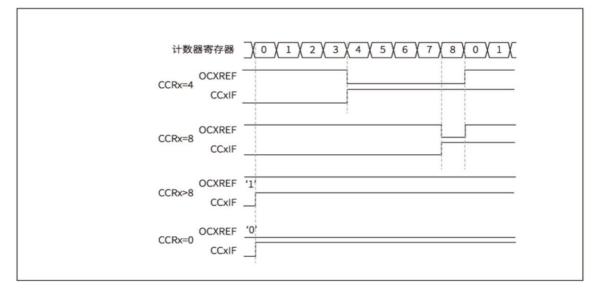

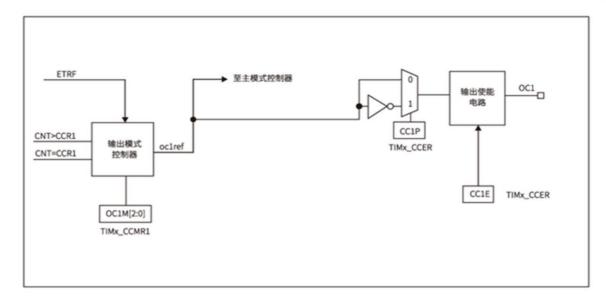

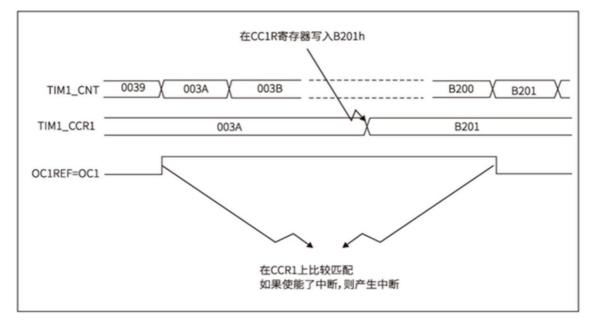

| 12.3.9 Output Compare Mode                                 |     |

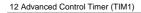

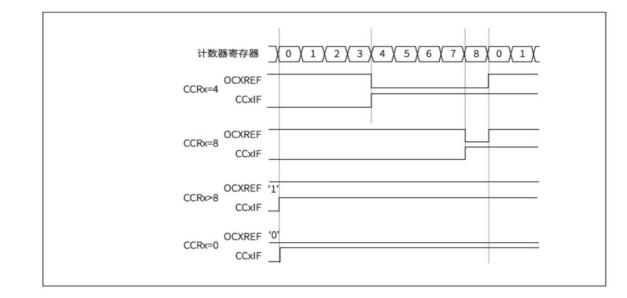

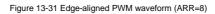

| 12.3.10 PWM mode                                           |     |

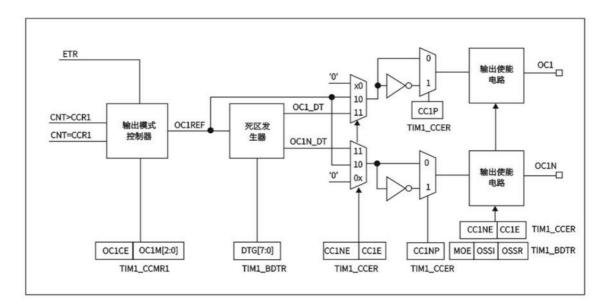

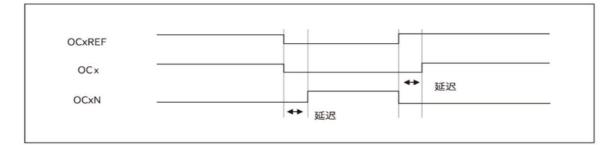

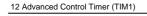

| 12.3.11 Complementary output and dead-time insertion       |     |

| 12.3.12 Using the brake function                           |     |

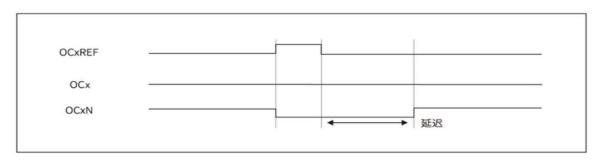

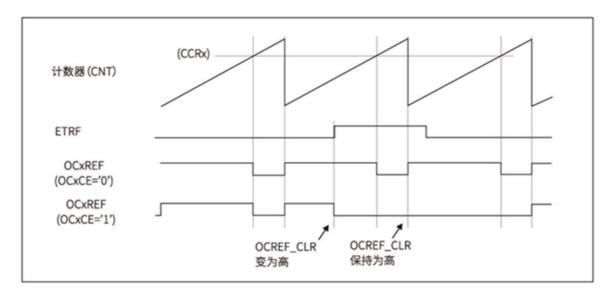

| 12.3.13 Clearing the OCxREF signal on an external event    |     |

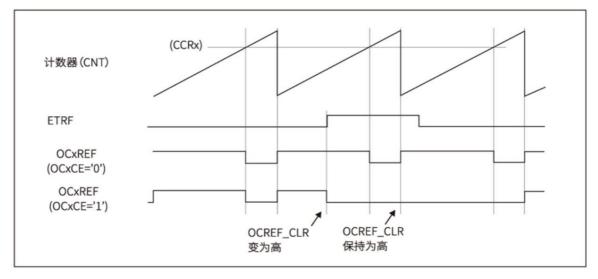

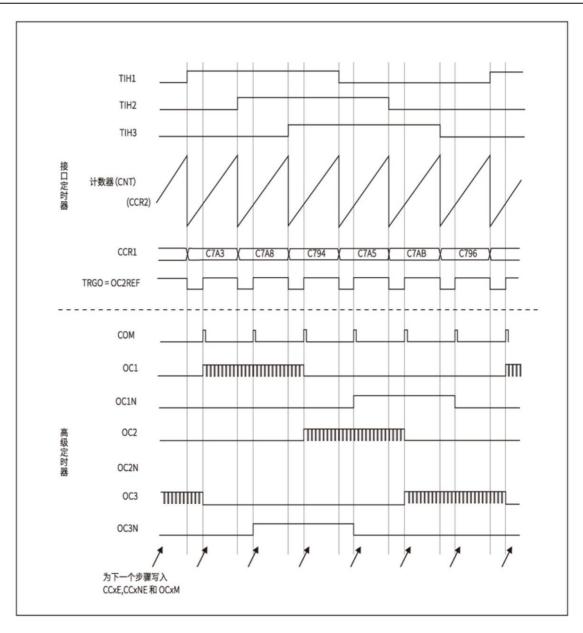

| 12.3.14 Generate six-step PWM output                       | 190 |

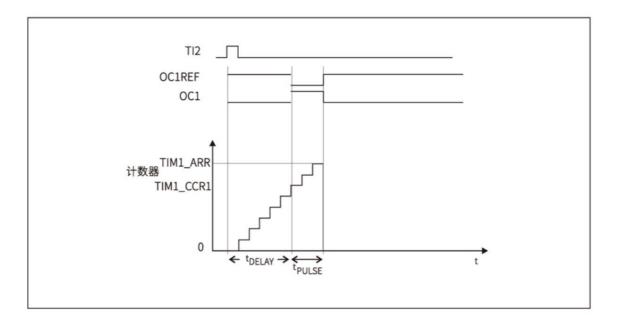

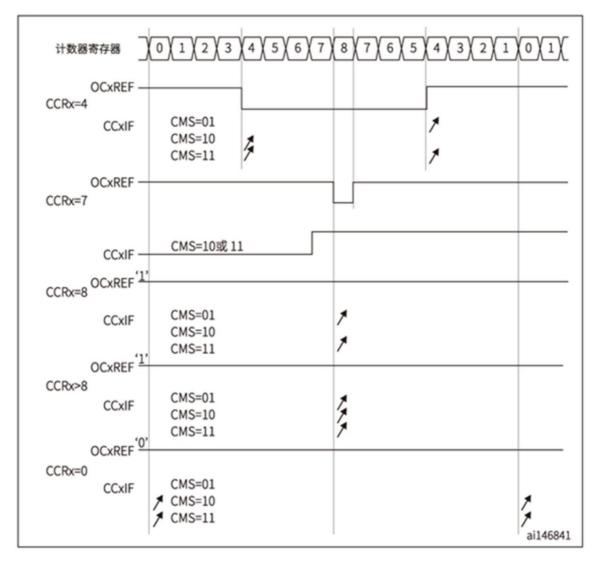

| 12.3.15 Single Pulse Mode                                  | 191 |

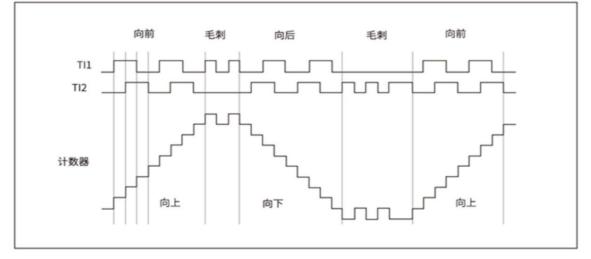

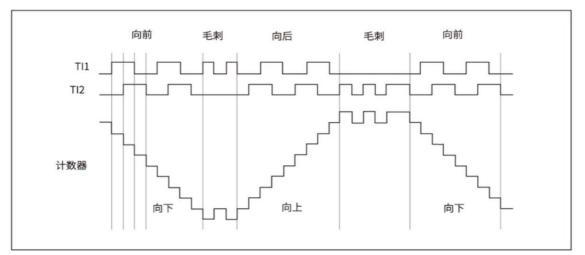

| 12.3.16 Encoder interface mode                             | 193 |

| 12.3.17 Timer input XOR function                           | 195 |

| 12.3.18 Interface with Hall sensor                         | 195 |

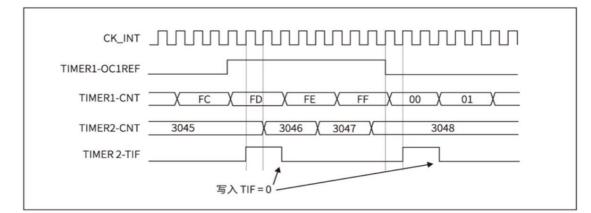

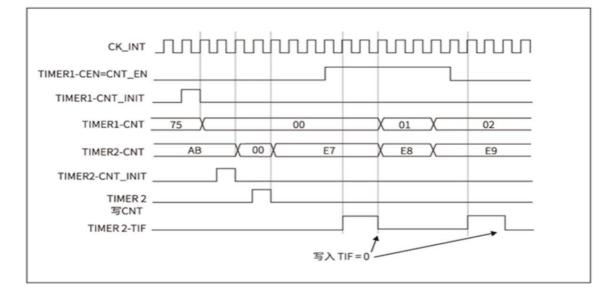

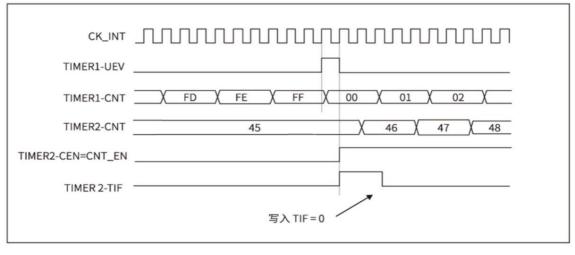

| 12.3.19 Synchronization of TIM1 timer and external trigger | 197 |

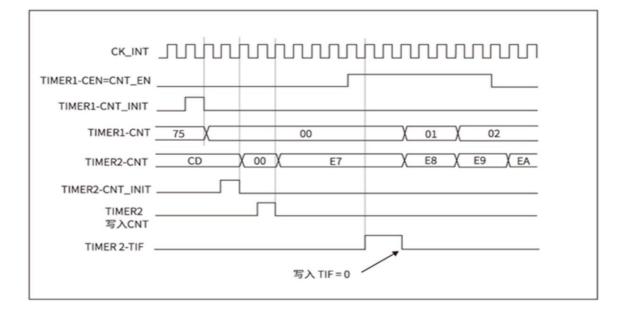

| 12.3.20 Timer Synchronization                              | 200 |

| 12.3.21 Debug mode                                         |     |

| 12.4 TIM1 register list                                    | 201 |

| 12.5 TIM1 register description                             |     |

| 12.5.1 TIM1 Control Register 1 (TIM1_CR1)                  |     |

| 12.5.2 TIM1 Control Register 2 (TIM1_CR2)                  |     |

| 12.5.3 TIM1 slave mode control register (TIM1_SMCR)        |     |

| 12.5.4 TIM1 interrupt enable register (TIM1_DIER)          | 208 |

| 12.5.5 TIM1 Status Register (TIM1_SR)                      | 209 |

| 12.5.6 TIM1 event generation register (TIM1_EGR)           | 211 |

| 12.5.7 TIM1 Capture/Compare Mode Register 1 (TIM1_CCMR1)   | 212 |

| 12.5.8 TIM1 Capture/Compare Mode Register 2 (TIM1_CCMR2)   | 215 |

| 12.5.9 TIM1 capture/compare enable register (TIM1_CCER)    | 217 |

| 12.5.10 TIM1 counter (TIM1_CNT)                            | 219 |

| 12.511 TM1 Auto-Reload Register (TM1_ARR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 12.5.11 TIM1 Prescaler (TIM1_PSC)                       | 210 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|-----|

| 12.5.13 TIM1 Repeat Count Register (TIM1_CCR1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                         |     |

| 12.5.14 TIM1 capture/compare register 1 (TIM1_CCR1)       .221         12.5.15 TIM1 capture/compare register 2 (TIM1_CCR3)       .222         12.5.16 TIM1 capture/compare register 3 (TIM1_CCR4)       .222         12.5.17 TIM1 capture/compare register 4 (TIM1_CCR4)       .222         12.5.17 TIM1 capture/compare register 4 (TIM1_CCR4)       .222         13.5.18 TIM1 Brake and Deadband Register (TIM1_BDTR)       .223         13 general-purpose timer (TIM2)       .225         13.1 Introduction to TIM2       .226         13.2 Main functions of TIM2       .226         13.3.1 Time base unit       .226         13.3.2 Counter Mode       .228         13.3.3 Clock selection       .236         13.3.4 Capture/Compare Channels       .239         13.3.5 Input capture mode       .241         13.3.6 PVM input mode       .241         13.3.7 Forced output mode       .245         13.3.10 Single Pulse Mode       .245         13.3.11 Clearing the OCxREF signal on an external event       .249         13.3.12 Encoder interface mode       .250         13.3.13 Timer input XOR function       .252         13.3.14 Synchronization of Timer and External Trigger       .252 | 12.5.12 TIM1 Auto-Reload Register (TIM1_ARR)            | 220 |

| 12.5.15 TIM1 capture/compare register 2 (TIM1_CCR2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 12.5.13 TIM1 Repeat Count Register (TIM1_RCR)           |     |

| 12.5.16 TIM1 capture/compare register 3 (TIM1_CCR3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 12.5.14 TIM1 capture/compare register 1 (TIM1_CCR1)     | 221 |

| 12.5.17 TIM1 capture/compare register 4 (TIM1_CCR4)       222         12.5.18 TIM1 Brake and Deadband Register (TIM1_BDTR)       223         13 general-purpose timer (TIM2)       225         13.1 Introduction to TIM2       225         13.2 Main functions of TIM2       225         13.3 TIM2 Function Description       226         13.3.1 Time base unit       226         13.3.2 Counter Mode       228         13.3.3 Clock selection       236         13.3.4 Capture/Compare Channels       239         13.3.5 Input capture mode       241         13.3.6 Input capture mode       242         13.3.7 Forced output mode       243         13.3.8 Output Compare Mode       244         13.3.9 PWM mode       245         13.3.11 Clearing the OCxREF signal on an external event       249         13.3.12 Encoder interface mode       250         13.3.14 Synchronization of Timer and External Trigger       252                                                                                                                                                                                                                                                                         | 12.5.15 TIM1 capture/compare register 2 (TIM1_CCR2)     | 221 |

| 12.5.18 TIM1 Brake and Deadband Register (TIM1_BDTR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 12.5.16 TIM1 capture/compare register 3 (TIM1_CCR3)     | 222 |

| 13 general-purpose timer (TIM2)       225         13.1 Introduction to TIM2       225         13.2 Main functions of TIM2       225         13.3 TIM2 Function Description       226         13.3 Time base unit       226         13.3.2 Counter Mode       228         13.3.3 Clock selection       236         13.4 Capture/Compare Channels       239         13.3.5 Input capture mode       241         13.3.6 PWM input mode       242         13.3.7 Forced output mode       244         13.3.8 Output Compare Mode       244         13.3.9 PWM mode       245         13.3.10 Single Pulse Mode       248         13.3.11 Clearing the OCxREF signal on an external event       249         13.3.12 Encoder interface mode       250         13.3.14 Synchronization of Timer and External Trigger.       252                                                                                                                                                                                                                                                                                                                                                                                 | 12.5.17 TIM1 capture/compare register 4 (TIM1_CCR4)     | 222 |

| 13.1 Introduction to TIM2       225         13.2 Main functions of TIM2       225         13.3 TIM2 Function Description       226         13.3.1 Time base unit       226         13.3.2 Counter Mode       228         13.3.3 Clock selection       236         13.3.4 Capture/Compare Channels       239         13.3.5 Input capture mode       241         13.3.6 PWM input mode       242         13.3.7 Forced output mode       243         13.3.8 Output Compare Mode       243         13.3.9 PWM mode       244         13.3.10 Single Pulse Mode       248         13.3.11 Clearing the OCxREF signal on an external event       249         13.3.12 Encoder interface mode       250         13.3.13 Timer input XOR function       252         13.3.14 Synchronization of Timer and External Trigger.       252                                                                                                                                                                                                                                                                                                                                                                            | 12.5.18 TIM1 Brake and Deadband Register (TIM1_BDTR)    | 223 |

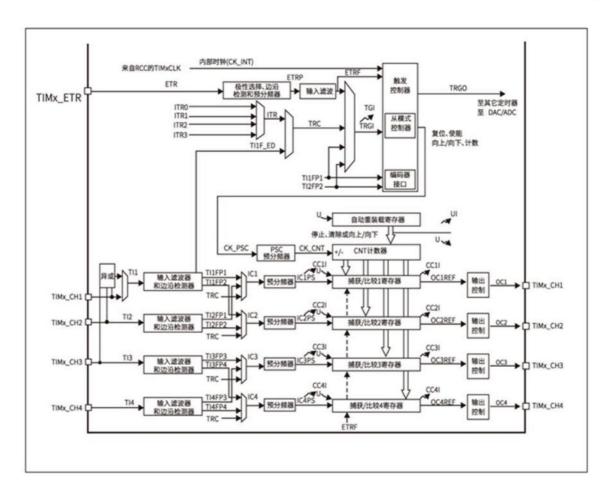

| 13.2 Main functions of TIM2.       225         13.3 TIM2 Function Description.       226         13.3.1 Time base unit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 13 general-purpose timer (TIM2)                         | 225 |

| 13.3 TIM2 Function Description.       226         13.3.1 Time base unit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 13.1 Introduction to TIM2                               | 225 |

| 13.3.1 Time base unit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 13.2 Main functions of TIM2                             | 225 |

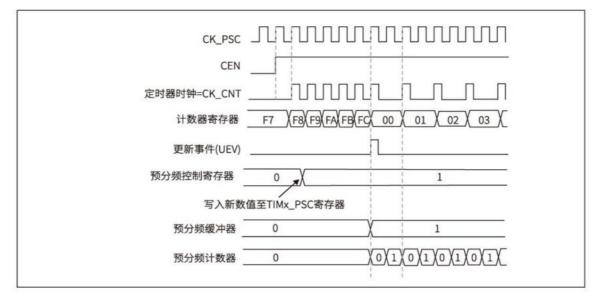

| 13.3.2 Counter Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 13.3 TIM2 Function Description                          | 226 |

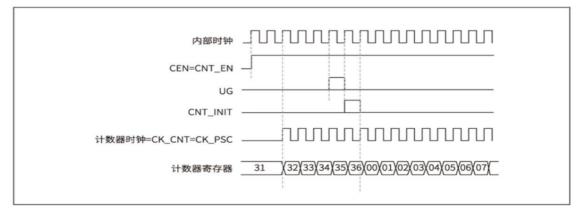

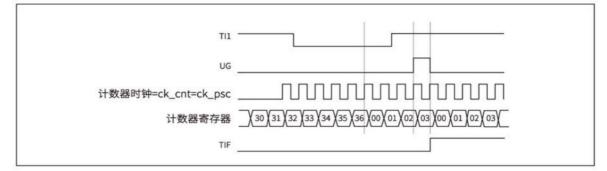

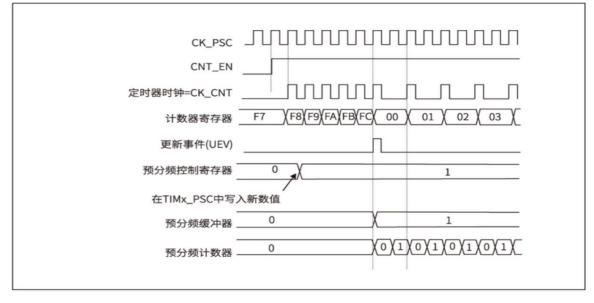

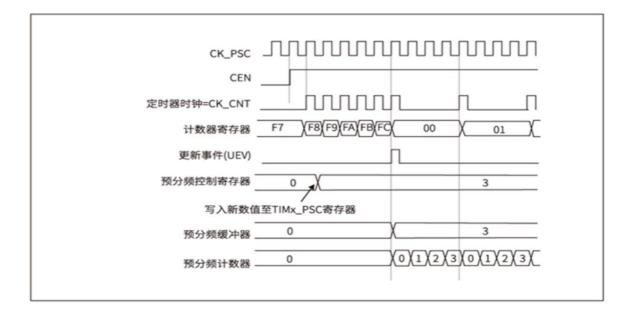

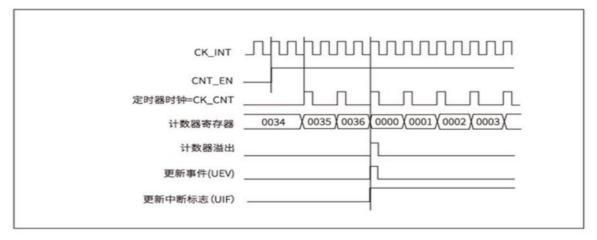

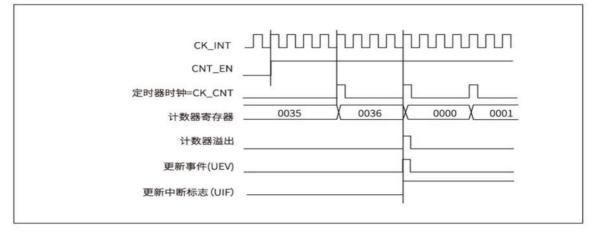

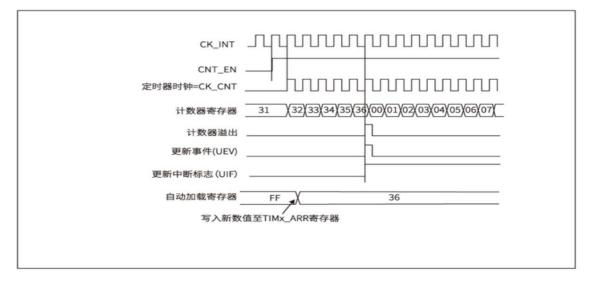

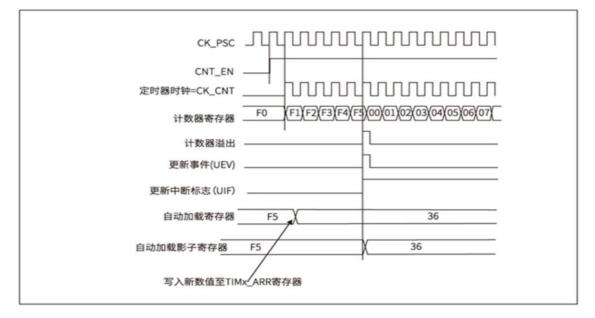

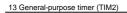

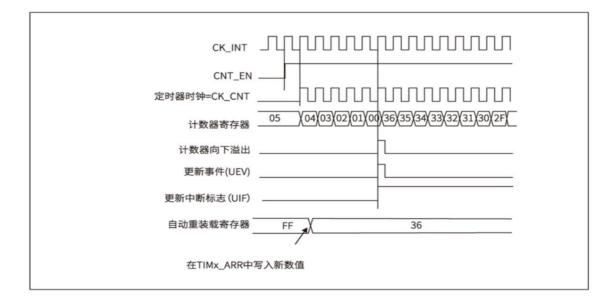

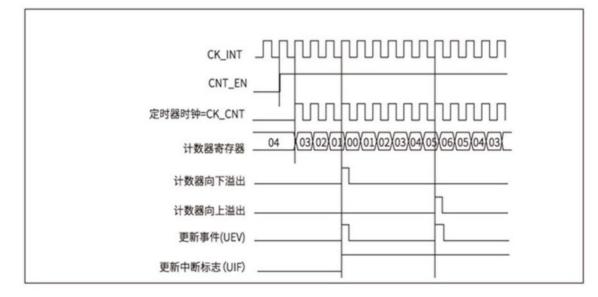

| 13.3.3 Clock selection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 13.3.1 Time base unit                                   | 226 |

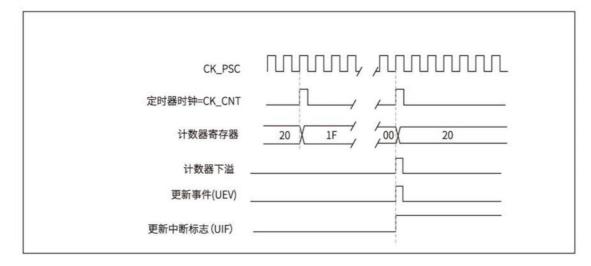

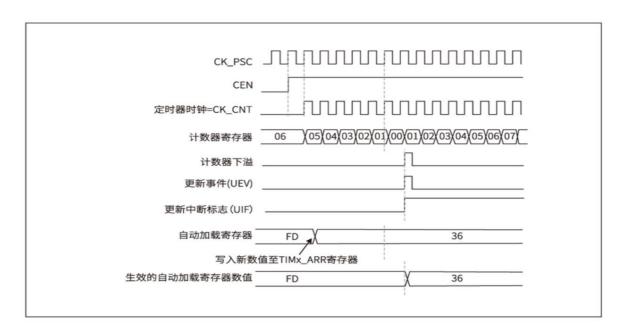

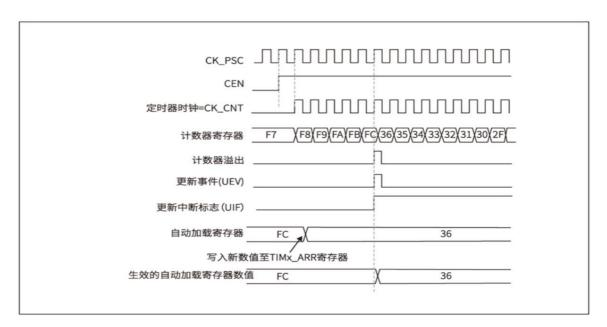

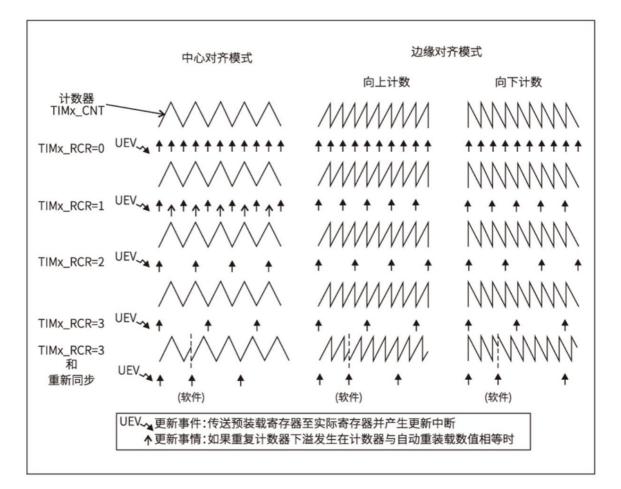

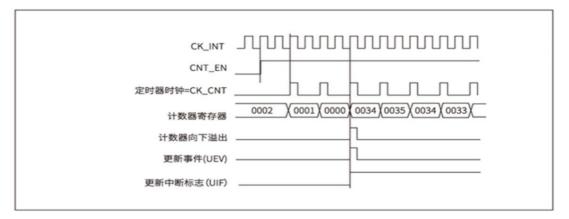

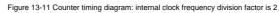

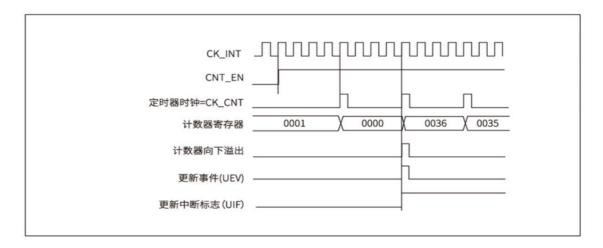

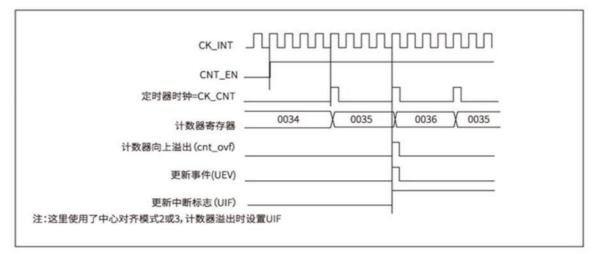

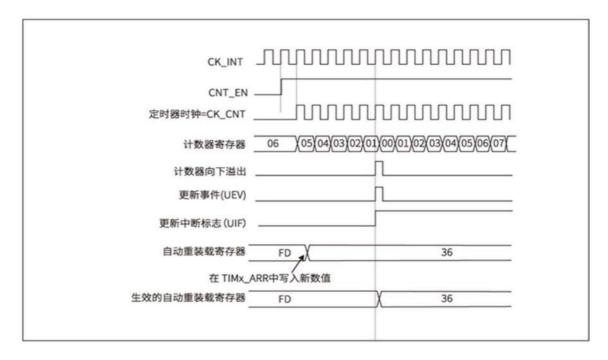

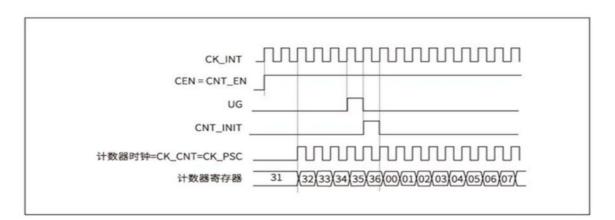

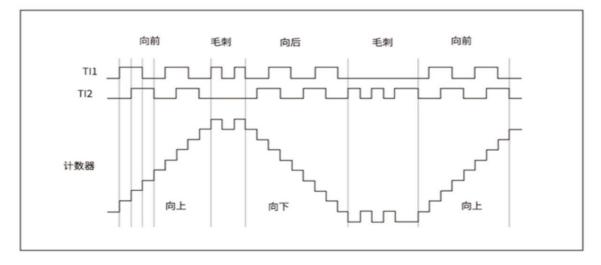

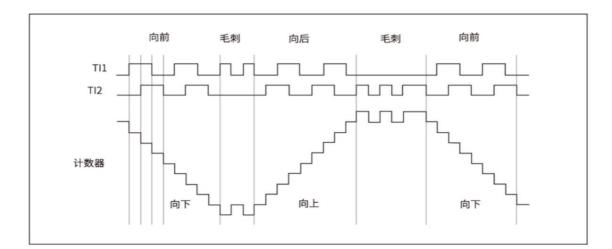

| 13.3.4 Capture/Compare Channels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 13.3.2 Counter Mode                                     | 228 |

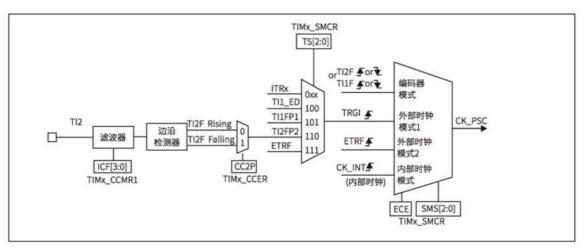

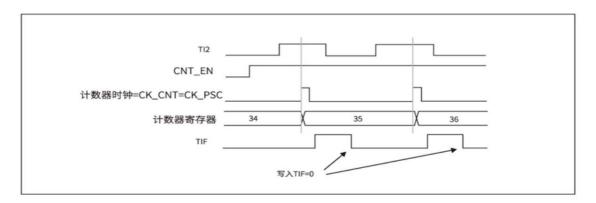

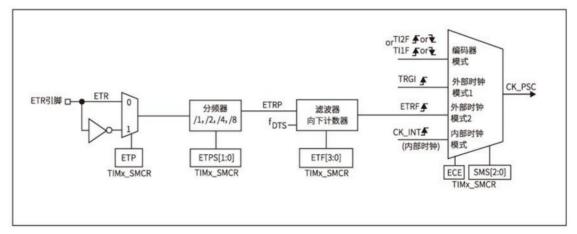

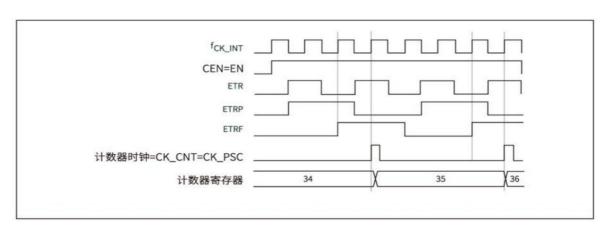

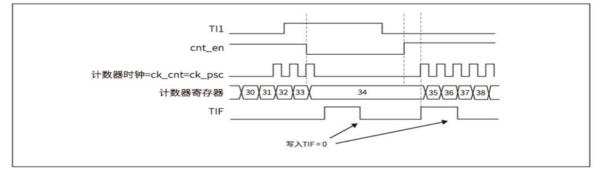

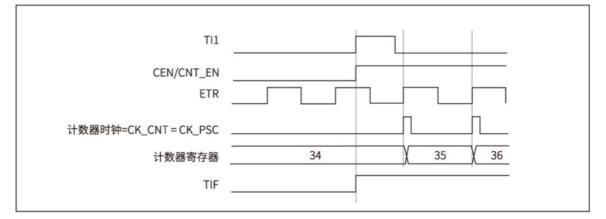

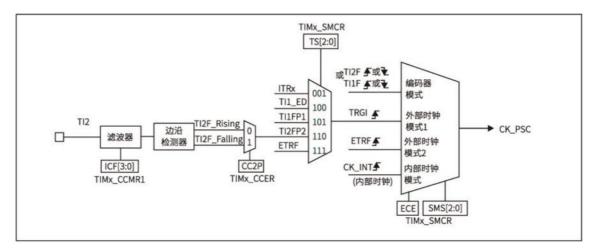

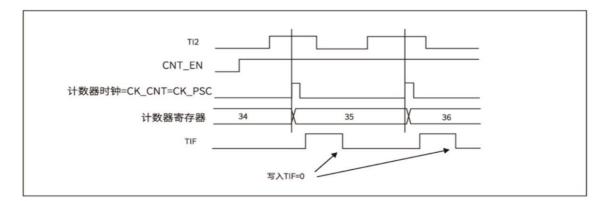

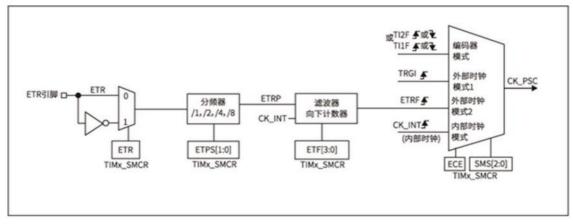

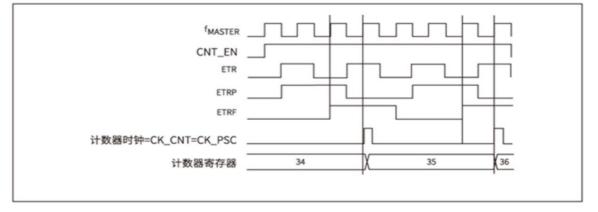

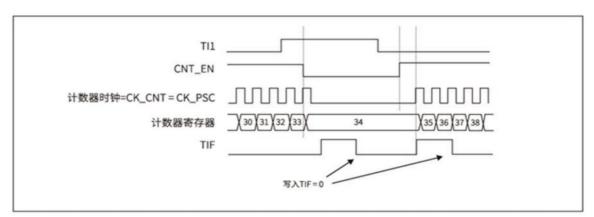

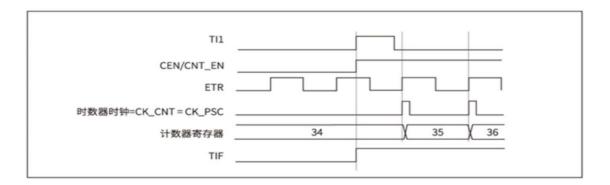

| 13.3.5 Input capture mode.       .241         13.3.6 PWM input mode.       .242         13.3.7 Forced output mode.       .243         13.3.8 Output Compare Mode.       .244         13.3.9 PWM mode.       .245         13.3.10 Single Pulse Mode       .248         13.3.11 Clearing the OCxREF signal on an external event.       .249         13.3.12 Encoder interface mode.       .250         13.3.13 Timer input XOR function       .252         13.3.14 Synchronization of Timer and External Trigger.       .252                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 13.3.3 Clock selection                                  | 236 |

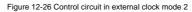

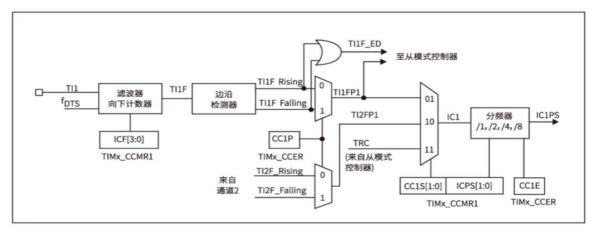

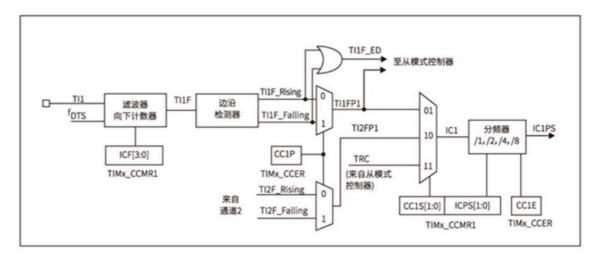

| 13.3.6 PWM input mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 13.3.4 Capture/Compare Channels                         | 239 |

| 13.3.7 Forced output mode24313.3.8 Output Compare Mode24413.3.9 PWM mode24513.3.10 Single Pulse Mode.24813.3.11 Clearing the OCxREF signal on an external event24913.3.12 Encoder interface mode25013.3.13 Timer input XOR function.25213.3.14 Synchronization of Timer and External Trigger252                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 13.3.5 Input capture mode                               | 241 |

| 13.3.8 Output Compare Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 13.3.6 PWM input mode                                   | 242 |

| 13.3.9 PWM mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 13.3.7 Forced output mode                               | 243 |

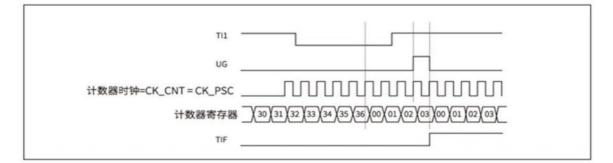

| 13.3.10 Single Pulse Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 13.3.8 Output Compare Mode                              | 244 |

| 13.3.11 Clearing the OCxREF signal on an external event.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 13.3.9 PWM mode                                         | 245 |

| 13.3.12 Encoder interface mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 13.3.10 Single Pulse Mode                               | 248 |

| 13.3.13 Timer input XOR function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 13.3.11 Clearing the OCxREF signal on an external event | 249 |

| 13.3.14 Synchronization of Timer and External Trigger252                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 13.3.12 Encoder interface mode                          | 250 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 13.3.13 Timer input XOR function                        | 252 |

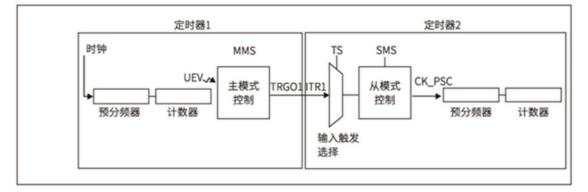

| 13.3.15 Timer Synchronization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 13.3.14 Synchronization of Timer and External Trigger   | 252 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 13.3.15 Timer Synchronization                           | 255 |

|                                                                       | <u>28</u> |

|-----------------------------------------------------------------------|-----------|

| 13.3.16 Debug mode                                                    |           |

| 13.4 TIM2 register list2                                              | 261       |

| 13.5 TIM2 register description                                        |           |

| 13.5.1 TIM2 Control Register 1 (TIM2_CR1)                             |           |

| 13.5.2 TIM2 Control Register 2 (TIM2_CR2)                             |           |

| 13.5.3 TIM2 Slave Mode Control Register (TIM2_SMCR)                   |           |

| 13.5.4 TIM2 interrupt enable register (TIM2_DIER)                     |           |

| 13.5.5 TIM2 Status Register (TIM2_SR)                                 |           |

| 13.5.6 TIM2 event generation register (TIM2_EGR)                      |           |

| 13.5.7 TIM2 Capture/Compare Mode Register 1 (TIM2_CCMR1)              |           |

| 13.5.8 TIM2 Capture/Compare Mode Register 2 (TIM2_CCMR2)              |           |

| 13.5.9 TIM2 capture/compare enable register (TIM2_CCER)               | 276       |

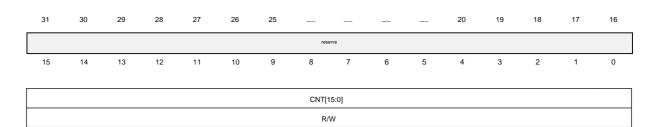

| 13.5.10 TIM2 counter (TIM2_CNT)                                       |           |

| 13.5.11 TIM2 Prescaler (TIM2_PSC)                                     |           |

| 13.5.12 TIM2 Auto-Reload Register (TIM2_ARR)                          |           |

| 13.5.13 TIM2 capture/compare register 1 (TIM2_CCR1)                   | 279       |

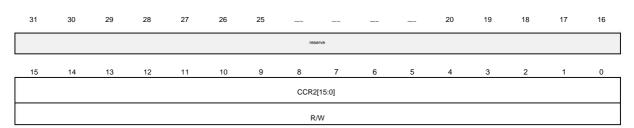

| 13.5.14 TIM2 Capture/Compare Register 2 (TIM2_CCR2)                   | 279       |

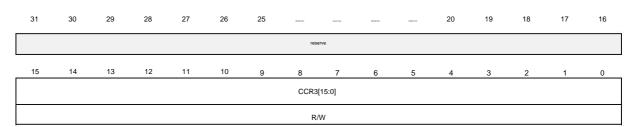

| 13.5.15 TIM2 Capture/Compare Register 3 (TIM2_CCR3)                   |           |

| 13.5.16 TIM2 Capture/Compare Register 4 (TIM2_CCR4)                   |           |

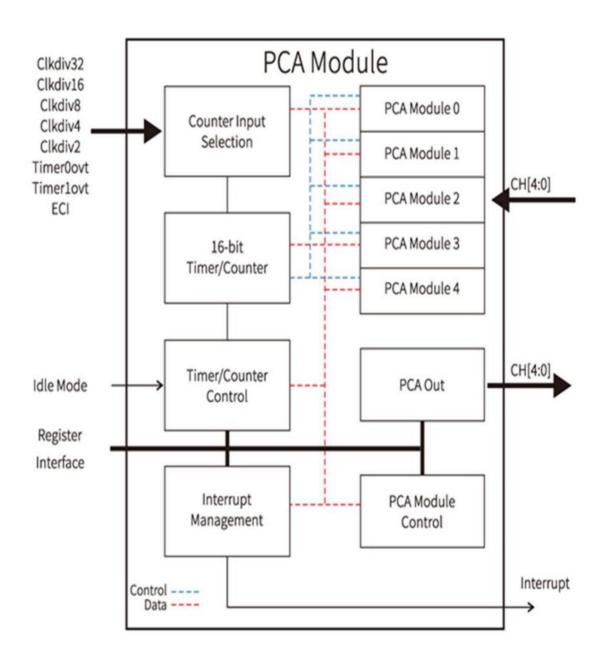

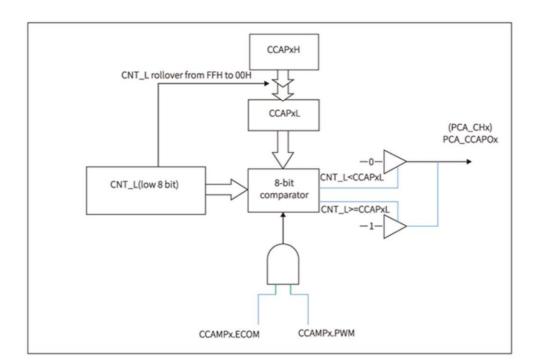

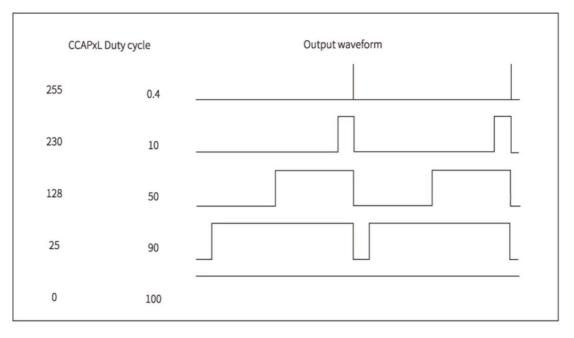

| 14 Programmable Count Array (PCA)                                     |           |

| 14.1 Introduction to PCA                                              |           |

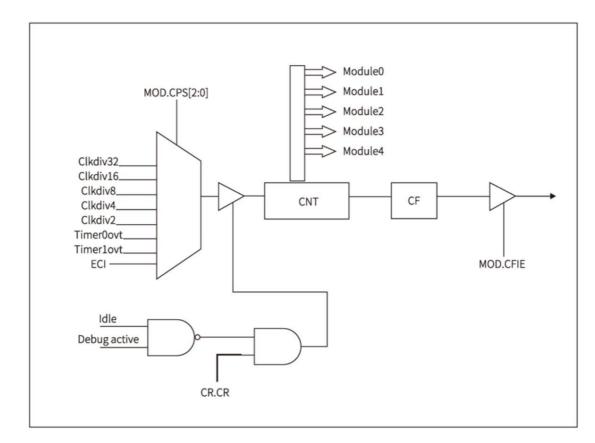

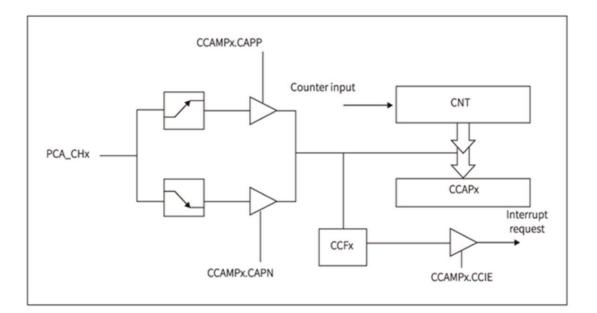

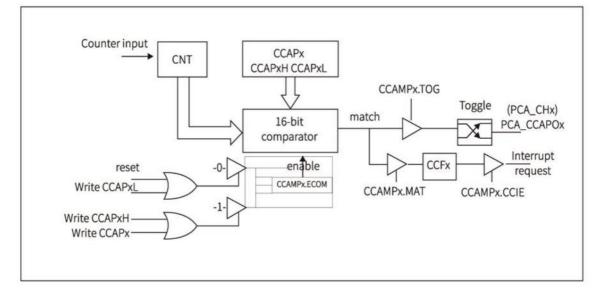

| 14.2 PCA Functional Description                                       |           |

| 14.2.1 PCA Timer/Counter                                              |           |

| 14.2.2 Capture function                                               |           |

| 14.2.3 PCA comparison function                                        |           |

| 14.3 Interconnection and control between PCA module and other modules |           |

\_\_\_\_\_

CX32L003 User Reference Manual

| 14.3.1 ECI interconnect                                                     |     |

|-----------------------------------------------------------------------------|-----|

| 14.3.2 PCACAP0                                                              | 287 |

| 14.3.3 PCACAP1/2/3/4                                                        | 287 |

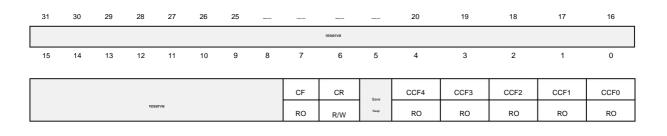

| 14.4 PCA register list                                                      | 288 |

| 14.5 Register description                                                   |     |

| 14.5.1 Control register (PCA_CR)                                            |     |

| 14.5.2 Mode register (PCA_MOD)                                              |     |

| 14.5.3 Count register (PCA_CNT)                                             | 291 |

| 14.5.4 Interrupt Clear Register (PCA_INTCLR)                                | 292 |

| 14.5.5 Compare capture mode registers (PCA_CCAPM0~4)                        | 293 |

| 14.5.6 Compare the lower 8 bits of the capture data register (PCA_CCAP0~4L) |     |

| 14.5.7 Compare the upper 8 bits of the capture data register (PCA_CCAP0~4H) | 295 |

| 14.5.8 Compare high-speed output flag register (PCA_CCAPO)                  | 296 |

| 14.5.9 Terminal Output Control Register (PCA_POCR)                          |     |

| 14.5.10 Compare capture 16-bit register (PCA_CCAP0~4)                       | 298 |

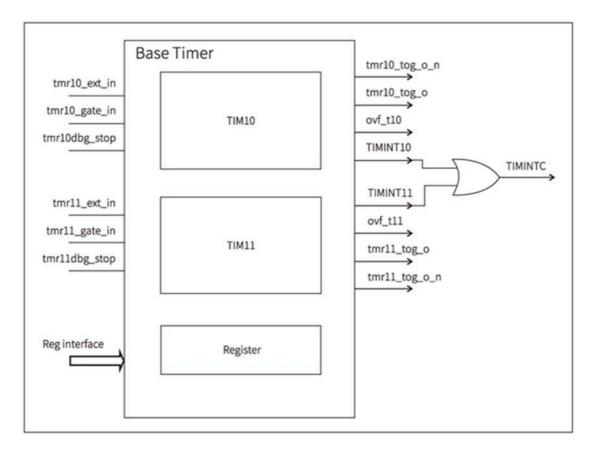

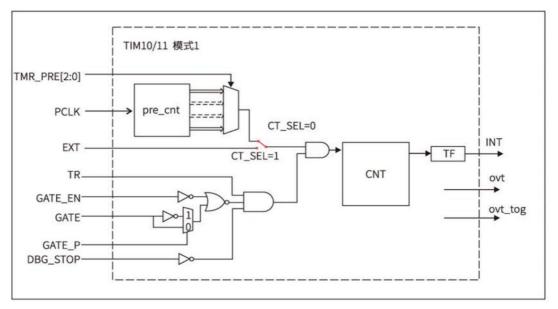

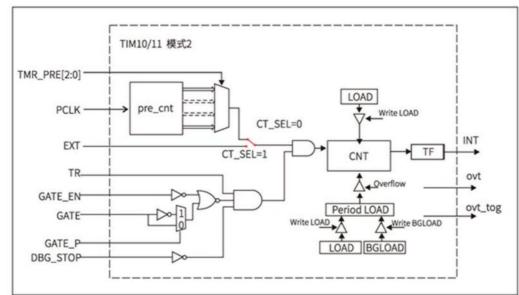

| 15 Base Timer Base Timer (TIM10/TIM11)                                      | 299 |

| 15.1 Introduction to Base Timer                                             |     |

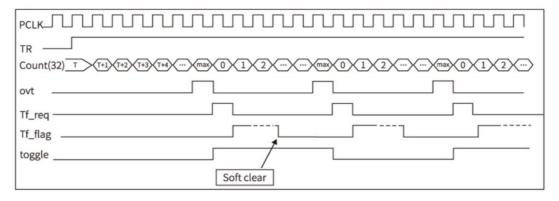

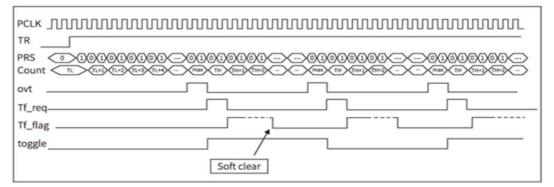

| 15.2 Base Timer Function Description                                        | 299 |

| 15.2.1 Counting function                                                    |     |

| 15.2.2 Timing function                                                      |     |

| 15.2.3 Buzzer function                                                      |     |

| 15.3 Base Timer Interconnection                                             | 303 |

| 15.3.1 GATE interconnection                                                 |     |

| 15.3.2 Toggle output interconnection                                        |     |

| 15.4 Base Timer register list                                               | 304 |

| 15.5 Base Timer register description                                        |     |

| 15.5.1 Control register (TIMx_CR)                          |     | 5     |       |

|------------------------------------------------------------|-----|-------|-------|

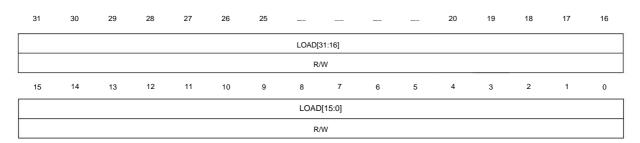

| 15.5.2 Immediate reload register (TIMx_LOAD)               |     | 306   |       |

| 15.5.3 Counter register (TIMx_CNT)                         | 306 |       |       |

| 15.5.4 Raw Interrupt Status Register (TIMx_RAWINTSR)       |     | 307   |       |

| 15.5.5 Interrupt flag register (TIMx_MSKINTSR)             | 308 |       |       |

| 15.5.6 Interrupt Clear Register (TIMx_INTCLR)              | 308 |       |       |

| 15.5.7 Period reload register (TIMx_BGLOAD)                | 309 |       |       |

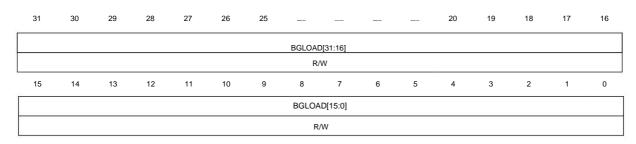

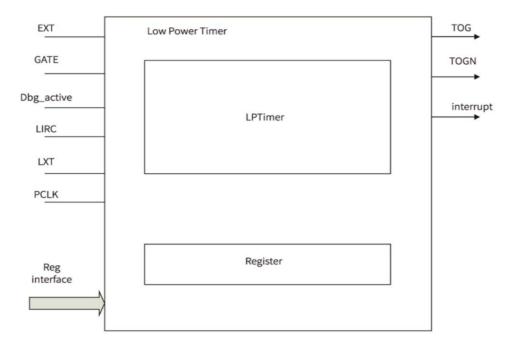

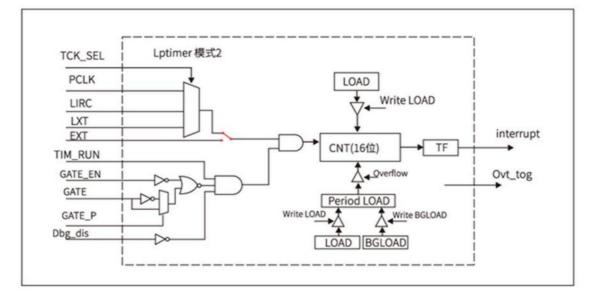

| 16 Low Power Timer (LPTIM)                                 |     |       | 310   |

| 16.1 LPTIM function description                            |     | 310   |       |

| 16.1.1 Counting function                                   |     | 312   |       |

| 16.1.2 Timing function                                     |     | 312   |       |

| 16.2 LPTIM Interconnection                                 |     |       | . 312 |

| 16.2.1 GATE interconnection                                |     | 312   |       |

| 16.2.2 EXT Interconnection                                 |     | 3     | 12    |

| 16.2.3 TOGGLE output interconnection                       |     |       | 312   |

| 16.3 List of LPTIM registers                               | 313 | i     |       |

| 16.4 LPTIM register description                            |     |       | . 314 |

| 16.4.1 LPTIM count value read-only register (LPTIM_CNTVAL) | 314 |       |       |

| 16.4.2 LPTIM Control Register (LPTIM_CR)                   | 315 |       |       |

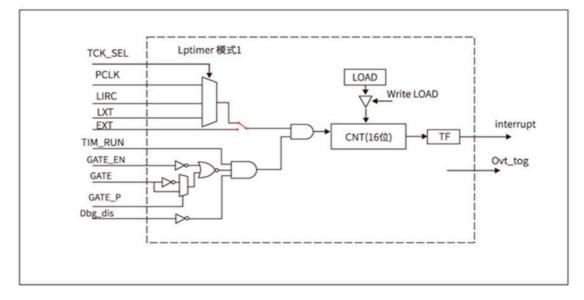

| 16.4.3 LPTIM Immediate Reload Register (LPTIM_LOAD)        |     | 316   |       |

| 16.4.4 LPTIM Interrupt Register (LPTIM_INTSR)              | 316 |       |       |

| 16.4.5 LPTIM Interrupt Register (LPTIM_INTCLR)             | 317 |       |       |

| 16.4.6 LPTIM Period Reload Register (LPTIM_BGLOAD)         |     | 317   |       |

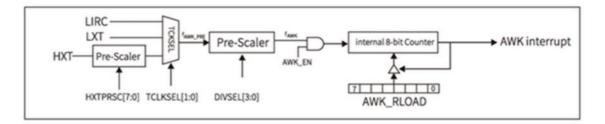

| 17 Self-wake-up timer (AWK)                                |     |       | 318   |

| 17.1 Register list                                         |     | . 319 |       |

| 17.2 Register description                                  |     |       | 320   |

| 17.2.1 Self-wake-up timer control register (AWK_CR)                                                                                                                                                                                                                       |         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 17.2.2 Self-wake-up timer reload data register (AWK_RLOAD)                                                                                                                                                                                                                |         |

| 17.2.3 Self-wake-up timer status register (AWK_SR)                                                                                                                                                                                                                        |         |

| 17.2.4 Self-wake-up interrupt clear register (AWK_INTCLR)                                                                                                                                                                                                                 |         |

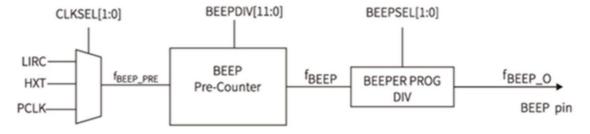

| 18 Buzzer (BEEP)                                                                                                                                                                                                                                                          | 322     |

| 18.1 Introduction                                                                                                                                                                                                                                                         |         |

| 18.2 Function description                                                                                                                                                                                                                                                 |         |

| 18.2.1 Buzzer operation                                                                                                                                                                                                                                                   |         |

| 18.2.2 Buzzer Calibration                                                                                                                                                                                                                                                 |         |

| 18.3 Register list                                                                                                                                                                                                                                                        | 323     |